**Communication Solutions**

Edition 2006-08-16

Published by Infineon Technologies AG 81726 München, Germany © Infineon Technologies AG 2006. All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie"). With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

VINETIC®-CPE Voice over IP Processor for Customer Premises Equipment CONFIDENTIAL

Revision History: 2006-08-16, Revision 1.0

Previous Version: VINETIC®-2CPE/-1CPE (PEB 3332/-3331) Version 2.1 Hardware Design Guide Rev. 2.0, 2006-03-14

| Page    | Subjects (major changes since last revision)                                    |  |

|---------|---------------------------------------------------------------------------------|--|

| Page 31 | Figure 19 is updated                                                            |  |

| Page 36 | 6 Chapter 5.2.1 hints added for the placement of GR-909 resistors               |  |

| Page 39 | Routing for EAN, EAO, SWD, SENSE and VS added in Chapter 5.3                    |  |

| Page 32 | Value of blocking caps modified                                                 |  |

|         | The old chapters 5.5 (Dual Layout) and chapter 6 (Transition Guide) are removed |  |

|         |                                                                                 |  |

|         |                                                                                 |  |

|         |                                                                                 |  |

|         |                                                                                 |  |

#### **Trademarks**

ABM®, ACE®, AOP®, Arcofi®, ASM®, ASP®, BlueMoon®, BlueNIX®, C166®, DuSLIC®, ELIC®, Epic®, FALC®, GEMINAX®, Idec®, INCA®, IOM®, Ipat®-2, IPVD®, Isac®, Itac®, IWE®, IWORX®, M-GOLD®, MUSAC®, MuSLIC®, OCTALFALC®, OCTAT®, POTSWIRE®, QUADFALC®, QUAT®, SCOUT®, SCT®, SEROCCO®, S-GOLD®, SICAT®, SICOFI®, SIDEC®, SIEGET®, SLICOFI®, SMARTI®, SOCRATES®, VDSLite®, VINETIC®, 10BaseS® are registered trademarks of Infineon Technologies AG.

ConverGate<sup>™</sup>, DIGITAPE<sup>™</sup>, DUALFALC<sup>™</sup>, EasyPort<sup>™</sup>, S-GOLDIte<sup>™</sup>, S-GOLD2<sup>™</sup>, S-GOLD3<sup>™</sup>, VINAX<sup>™</sup>, WildPass<sup>™</sup>, 10BaseV<sup>™</sup>, 10BaseV<sup>™</sup> are trademarks of Infineon Technologies AG.

Microsoft<sup>®</sup> and Visio<sup>®</sup> are registered trademarks of Microsoft Corporation. Linux<sup>®</sup> is a registered trademark of Linus Torvalds. FrameMaker<sup>®</sup> is a registered trademark of Adobe Systems Incorporated. APOXI<sup>®</sup> is a registered trademark of Comneon GmbH & Co. OHG. PrimeCell<sup>®</sup>, RealView<sup>®</sup>, ARM<sup>®</sup> are registered trademarks of ARM Limited. OakDSPCore<sup>®</sup>, TeakLite<sup>®</sup> DSP Core, OCEM<sup>®</sup> are registered trademarks of ParthusCeva Inc.

IndoorGPS™, GL-20000™, GL-LN-22™ are trademarks of Global Locate. ARM926EJ-S™, ADS™, Multi-ICE™ are trademarks of ARM Limited.

## **Table of Contents**

# **Table of Contents**

|                  | Table of Contents                                                      | . 4 |

|------------------|------------------------------------------------------------------------|-----|

|                  | List of Figures                                                        | . 6 |

|                  | List of Tables                                                         | . 7 |

|                  | Preface                                                                | . 8 |

|                  | General Design Overview                                                | . 9 |

| 2                | Design Guidelines for VINETIC®-2CPE/-1CPE                              | 10  |

| 2.1              | Interface Configurations                                               |     |

| 2.1.1            | Serial Micro Controller Interface Type: SCI + PCM                      |     |

| 2.1.2            | Parallel Interface Type: 8-bit INTEL Multiplexed Mode + PCM            |     |

| 2.1.3            | Parallel Interface Type: 8-bit INTEL Demultiplexed Mode + PCM          |     |

| 2.1.4            | Parallel Interface Type: 8-bit MOTOROLA Mode + PCM                     |     |

| 2.2              | Additional Circuitry for the Chip Select Signal                        |     |

| 2.3              | RDYQ Signal                                                            |     |

| 2.4<br>2.5       | Reset                                                                  |     |

| 2.5<br>2.5.1     | Application with Distributed Clocks (e.g. via PCM)                     |     |

| 2.5.1            | Local Clock Generation                                                 |     |

| 2.6              | PCM Interface                                                          |     |

| 2.7              | JTAG                                                                   |     |

| 2.8              | GPIOs                                                                  |     |

| 2.9              | Analog Interfaces                                                      |     |

| 2.9.1            | Signal Interfaces                                                      |     |

| 2.9.2            | Control Interfaces                                                     | 23  |

| 3                | Design Guidelines for SLICs                                            | 24  |

| 3.1              | VINETIC®-SLIC Interface                                                | 24  |

| 3.1.1            | Signal Interfaces                                                      | 24  |

| 3.1.2            | Influence of External Components                                       |     |

| 3.1.2.1          | External Components between SLIC and VINETIC®                          |     |

| 3.1.2.2          | C <sub>ITAC</sub>                                                      |     |

| 3.1.2.3          | C <sub>PRE</sub>                                                       |     |

| 3.1.2.4          | C <sub>REF</sub>                                                       |     |

| 3.1.2.5          | C <sub>DCLP</sub>                                                      |     |

| 3.2              | Tip-Ring Interface: $C_{STAB}$ , $R_{STAB}$ , $R_{PROT}$ and $C_{EMC}$ |     |

| 3.2.1            | C <sub>STAB</sub>                                                      |     |

| 3.2.2<br>3.2.3   | R <sub>STAB</sub>                                                      |     |

| 3.2.4            | R <sub>PROT</sub>                                                      |     |

| 3.3              | Additional Protection Devices at the Line                              |     |

| 3.4              | External Circuitry for GR-909 Support                                  |     |

| •                | Power Supply and Grounding                                             |     |

| •<br>1.1         | General Overview of Power and Ground Planes                            |     |

| +. ı<br>1.1.1    | Analog Power Plane                                                     |     |

| i. i. i<br>i.1.2 | Digital Power Plane                                                    |     |

| i.1.2            | Signal Ground Plane                                                    |     |

| I.1.4            | Chassis Ground Plane                                                   |     |

| 1.1.5            | Avoiding Loop Antenna Effect                                           |     |

7

| CONFIDENTIAL |                                                       | Table of Contents |

|--------------|-------------------------------------------------------|-------------------|

| 4.2          | VINETIC® Supply                                       |                   |

| 4.3          | SLIC Supply                                           |                   |

| 4.3.1        | SLIC-DC                                               |                   |

| 4.3.2        | SLIC-E                                                |                   |

| 4.4          | Supply Filtering                                      |                   |

| 4.4.1        | Decoupling of the VINETIC®-2CPE/-1CPE Supply Voltages |                   |

| 4.4.2        | PLL Supply Voltage                                    |                   |

| 4.4.3        | Decoupling of the SLIC-E Supply Voltages              |                   |

| 5            | Layout Guide                                          |                   |

| 5.1          | Layer Stack                                           |                   |

| 5.2          | Layout Recommendations                                |                   |

| 5.2.1        | Placement                                             |                   |

| 5.2.2        | Routing                                               |                   |

| 5.3          | Layout Hints for the SLIC-DC                          |                   |

| 5.4          | Layout Hints for the SLIC-E                           | 40                |

| 5.4.1        | Placement of Power Supply Components                  | 40                |

| 5.4.2        | Routing                                               | 40                |

| 5.4.3        | Cooling Area on PCB                                   | 40                |

| 6            | Summary and Design Checklist                          | 41                |

| 6.1          | Schematic Guidelines                                  | 41                |

| 6.1.1        | Power Supply                                          | 41                |

| 6.1.2        | VINETIC® Section                                      | 41                |

| 6.1.3        | SLIC Section                                          |                   |

| 6.2          | Layout Guidelines                                     | 42                |

| 6.2.1        | Placement, Layer Stack up, and the Routing Rules      |                   |

| 6.2.2        | Summary and Checklist Layout                          |                   |

| 6.2.2.1      | General Points                                        |                   |

| 6.2.2.2      | Digital Section and Signals                           |                   |

| 6.2.2.3      | Analog Sections and Signals                           | 42                |

**List of Figures**

# **List of Figures**

| Figure 1  | Interface Topology of a CPE with VINETIC®-2CPE/-1CPE                                  | . 9 |

|-----------|---------------------------------------------------------------------------------------|-----|

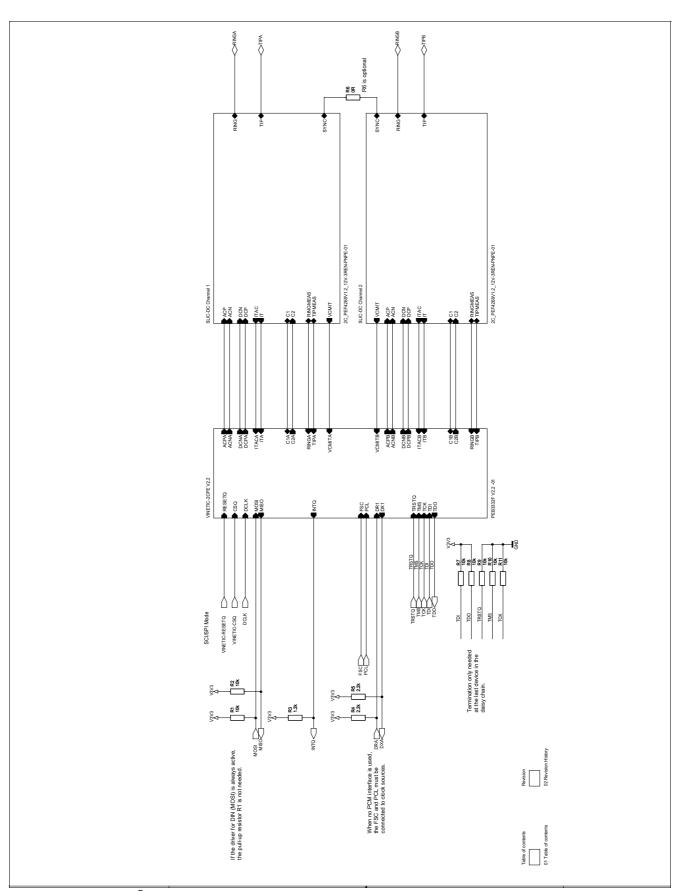

| Figure 2  | VINETIC®-2CPE/-1CPE in SCI/SPI Mode                                                   | 10  |

| Figure 3  | Parallel Interface Type: 8-bit INTEL Multiplexed Mode + PCM                           | 12  |

| Figure 4  | Parallel Interface Type: 8-bit INTEL Demultiplexed Mode + PCM                         | 13  |

| Figure 5  | VINETIC®-2CPE/-1CPE Connected to ADM5120                                              | 14  |

| Figure 6  | Parallel Interface Type: 8-bit MOTOROLA Mode + PCM                                    |     |

| Figure 7  | VINETIC®-2CPE/-1CPE Connected to MPC860                                               | 16  |

| Figure 8  | Additional Chip Select Logic for some Host Controllers                                | 17  |

| Figure 9  | PLL for Generation of PCM Clocks from one of two Reference Clocks                     | 18  |

| Figure 10 | Clock Distribution by Crystal Oscillator and Synchronous Divider                      |     |

| Figure 11 | Clock Distribution by Crystal and Ripple Counter                                      |     |

| Figure 12 | Internal PCM-Highway Connection                                                       | 20  |

| Figure 13 | PCM Highway and no Driver at +3.3 V PCM Highway                                       | 21  |

| Figure 14 | PCM Interface with Driver at +5 V PCM Highway                                         | 22  |

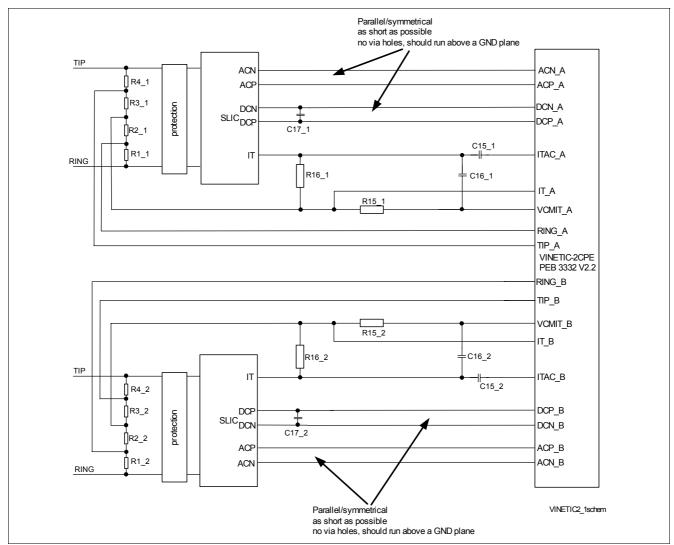

| Figure 15 | Interface between SLIC and VINETIC®                                                   | 24  |

| Figure 16 | Transversal Currents                                                                  | 25  |

| Figure 17 | Tip-Ring Interface                                                                    | 27  |

| Figure 18 | Line Testing Resistors at RING/TIP                                                    | 29  |

| Figure 19 | DC/DC Component Placement                                                             | 31  |

| Figure 20 | Analog Power Plane                                                                    | 31  |

| Figure 21 | Incorrect SLIC Decoupling                                                             | 34  |

| Figure 22 | Correct SLIC Decoupling                                                               | 35  |

| Figure 23 | Correct SLIC Decoupling for two Battery Supplies                                      | 35  |

| Figure 24 | Layer Stack Setup                                                                     | 36  |

| Figure 25 | Connections between the VINETIC®-2CPE/-1CPE and the SLIC-DC with External Components. | 38  |

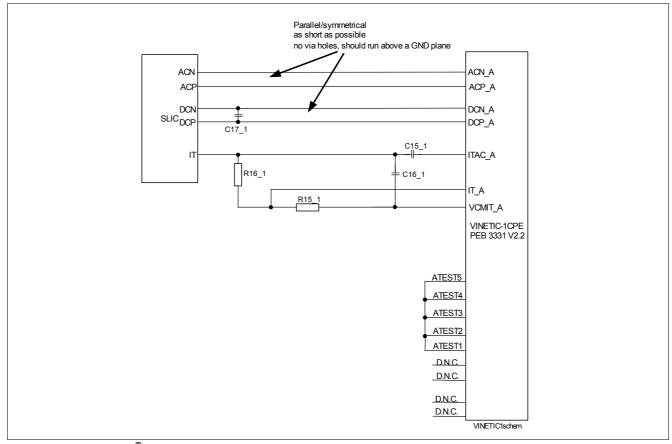

| Figure 26 | VINETIC®-1CPE Version 2.2 for one Channel                                             | 39  |

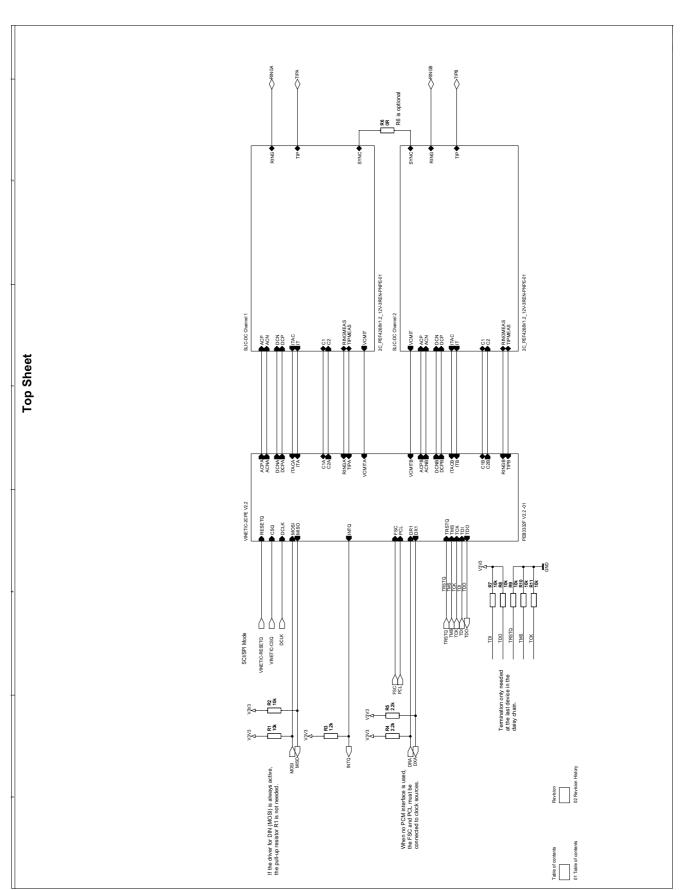

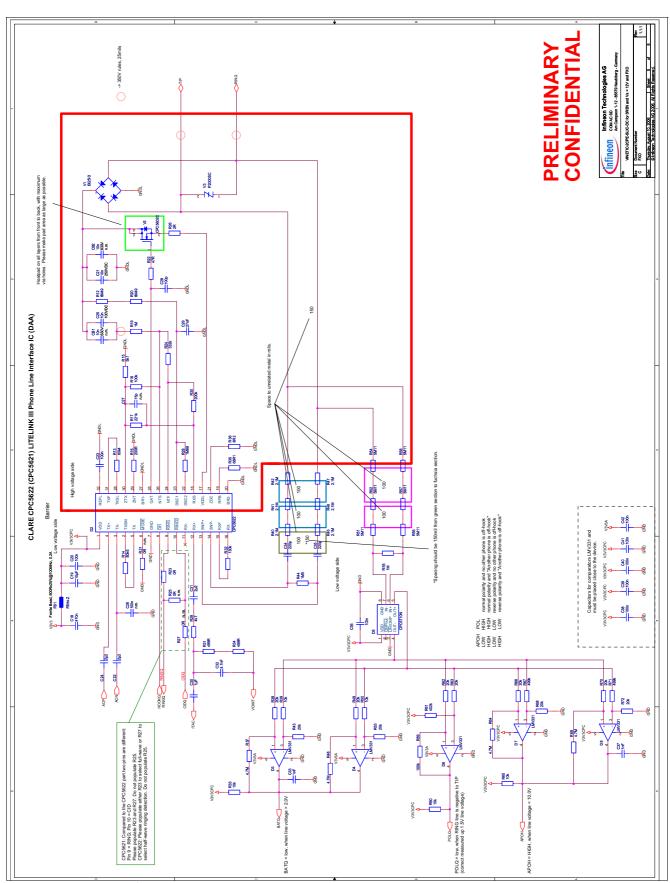

| Figure 27 | VINETIC®-2CPE Version 2.2, SLIC-DC Version 1.2 (Top Sheet)                            |     |

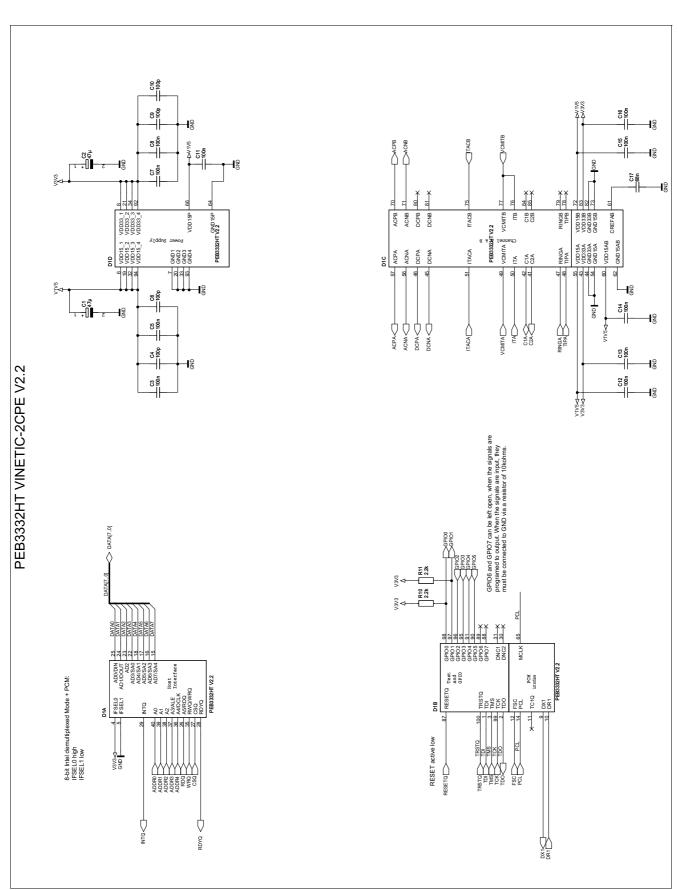

| Figure 28 | VINETIC®-2CPE Version 2.2 in SCI/SPI Mode                                             | 46  |

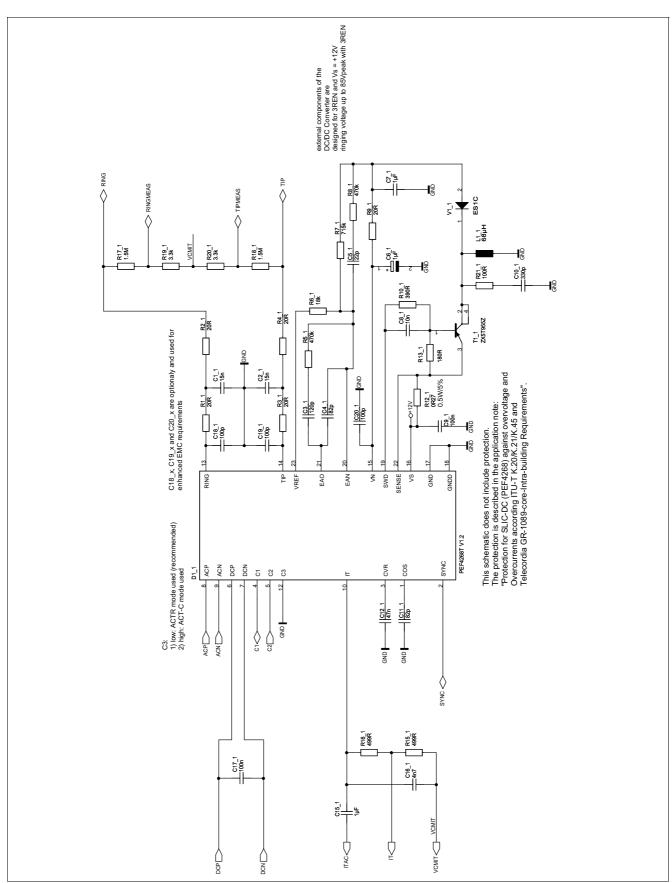

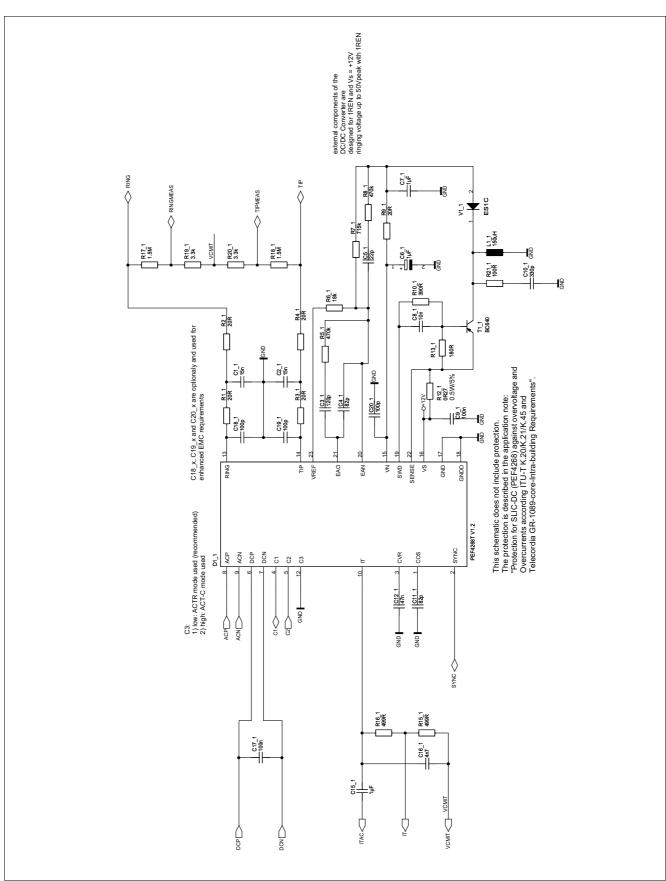

| Figure 29 | SLIC-DC Version 1.2 for 3 REN and +12 V Power Supply (Low Cost)                       | 47  |

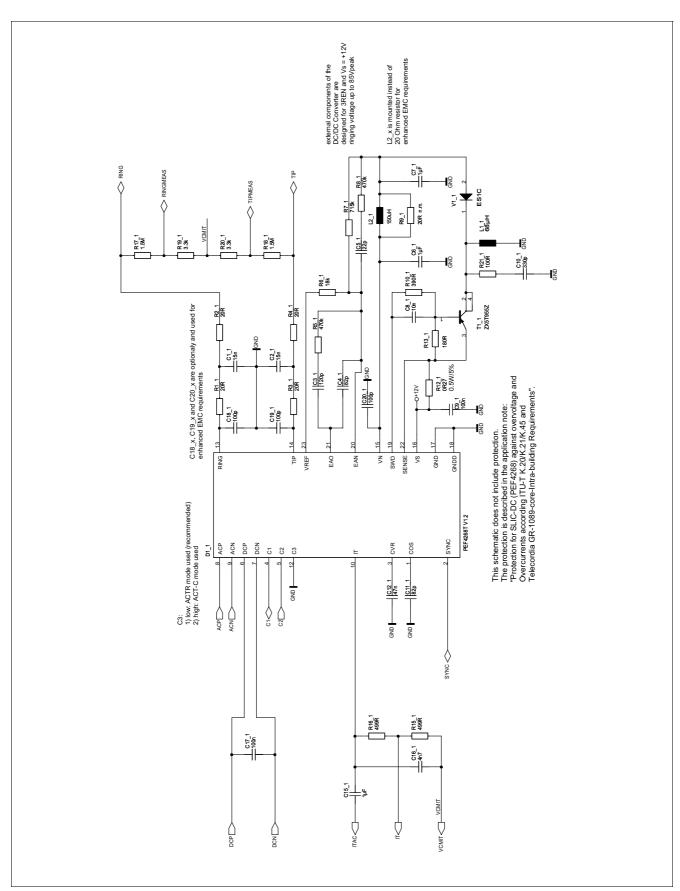

| Figure 30 | SLIC-DC Version 1.2 for 3 REN and +12 V Power Supply (Standard EU Market)             | 48  |

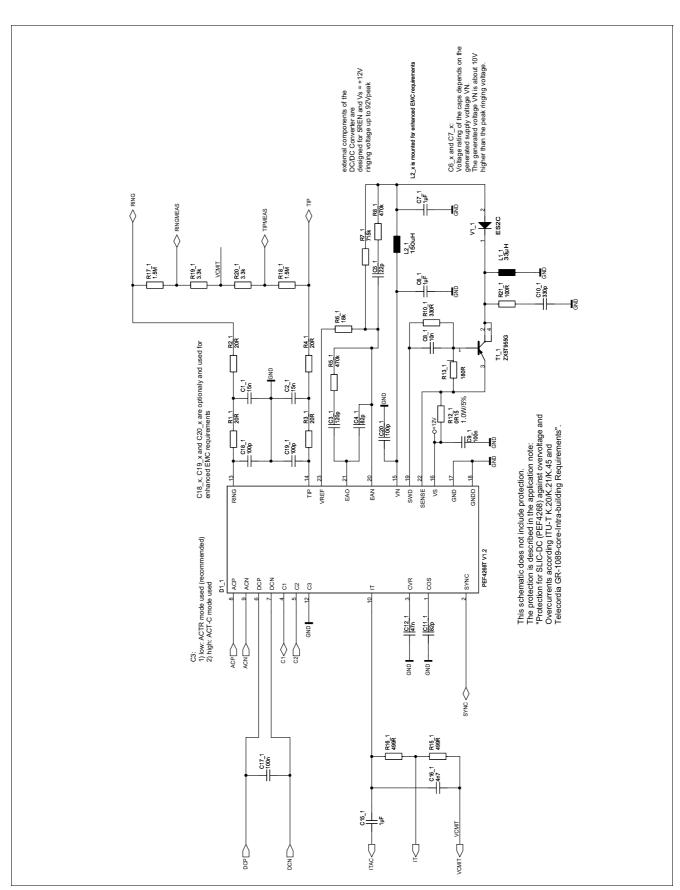

| Figure 31 | SLIC-DC Version 1.2 for 5 REN and +12 V Power Supply                                  | 49  |

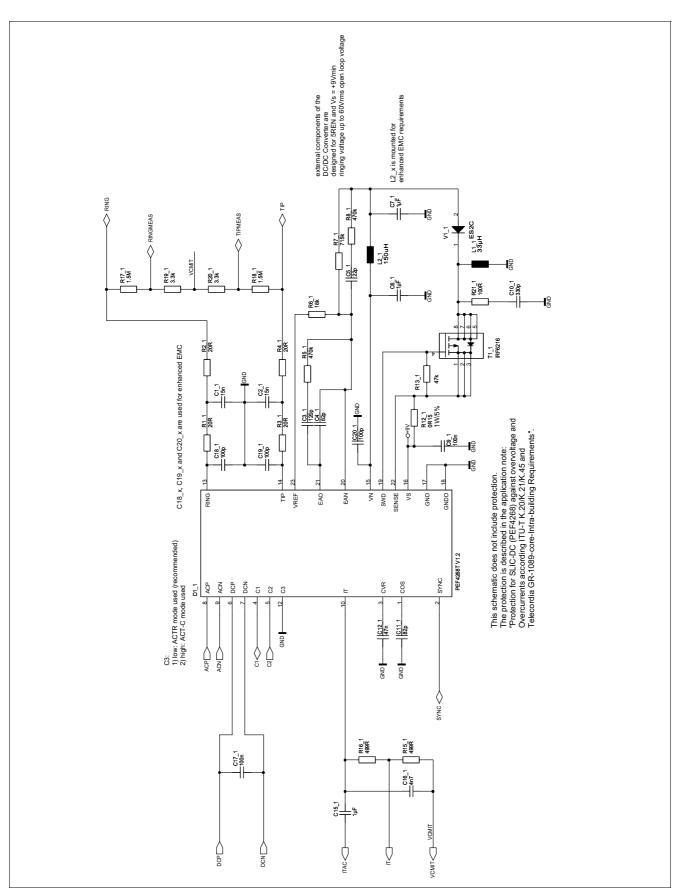

| Figure 32 | SLIC-DC for 5 REN and +9 Vmin Power Supply                                            | 50  |

| Figure 33 | SLIC-DC for 1 REN and +12 V Power Supply                                              | 51  |

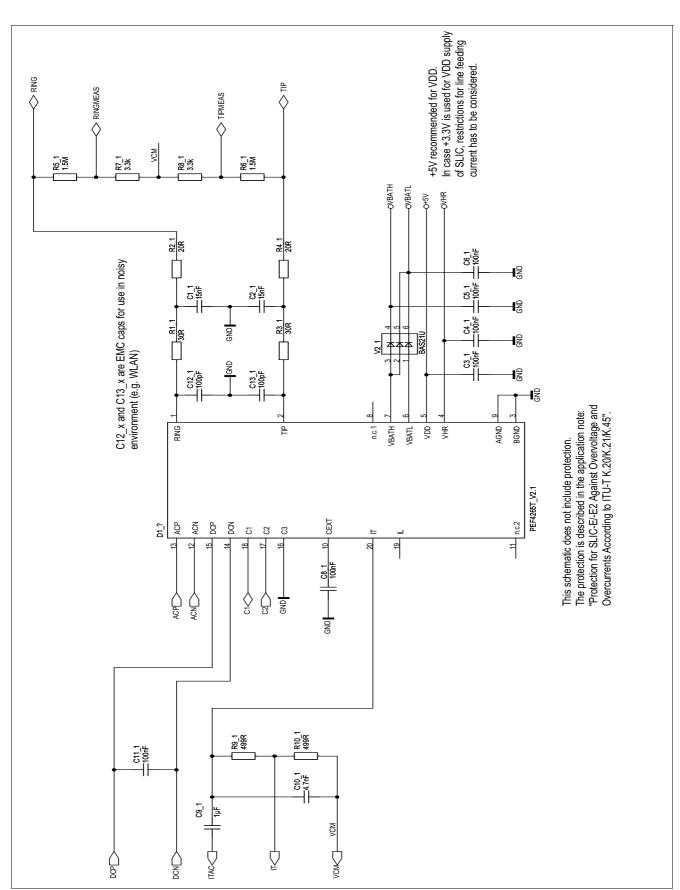

| Figure 34 | SLIC-E (PEF 4265 T) Version 2.1 Channel A                                             |     |

| Figure 35 | VINETIC®-2CPE Version 2.2 with DAA Functionality at Channel B (Top Sheet)             | 53  |

| Figure 36 | VINETIC®-2CPE Version 2.2 with DAA Functionality at Channel B (VINETIC®-2CPE Sheet)   | 54  |

| Figure 37 | VINETIC®-2CPE Version 2.2 with DAA Functionality at Channel B (DAA Sheet)             | 55  |

## CONFIDENTIAL

**List of Tables**

## **List of Tables**

| Table 1 | Data Bus Connection in 8-bit MOTOROLA Mode                     | 16 |

|---------|----------------------------------------------------------------|----|

| Table 2 | Mounting Option for an unused Channel                          | 38 |

| Table 3 | Ringer Load and Power Supply Voltage versus External Circuitry | 44 |

CONFIDENTIAL Preface

## **Preface**

The VINETIC®-2CPE/-1CPE Hardware Design Guide serves as a reference document for the design of applications using the VINETIC®-2CPE Version 2.2 or VINETIC®-1CPE Version 2.2 together with the SLIC-DC Version 2.1 and SLIC-E Version 2.1. The VINETIC® Chip Set Family allows easy integration of analog line POTS (Plain Old Telephony System) functions with additional enhanced DSP features.

This document is intended to help the reader become familiar with the VINETIC®-2CPE/-1CPE Version 2.2 devices and to accelerate the development process. This VINETIC®-2CPE/-1CPE Hardware Design Guide provides design and layout guidelines for achieving optimum performance for a POTS application. Following these guidelines helps to ensure a reliable design.

To simplify matters, the following synonyms are used:

VINETIC®:

Synonym used for the CODEC versions VINETIC®-2CPE/-1CPE Version 2.2.

SLIC:

Synonym used for the SLIC-DC Version 1.2 and the SLIC-E Version 2.1.

Attention: TSLIC-E (PEF 4365) is a dual channel version of the SLIC-E (PEF 4265) with identical technical specifications for each channel. Therefore, whenever SLIC-E is mentioned in the specification, TSLIC-E can also be deployed.

In order to simplify the usage of channel specific pin names within this document, in many cases only the short form for the pin names is used without endings indicating the specific channel A or B (\_A, \_B).

#### **Organization of this Document**

### **Chapter 1: General Design Overview**

General overview for system design with the VINETIC®-CPE Chip Set.

### Chapter 2: Design Guidelines for VINETIC®-2CPE/-1CPE

Schematic design practices are identified to prevent most common signal and noise issues. This includes signal termination, analog circuitry, and pull-up /-down resistors.

### **Chapter 3: Design Guidelines for SLICs**

Schematic design practices are identified to prevent most common signal and noise issues. This includes analog circuitry, packages and component values.

## **Chapter 4: Power Supply and Grounding**

This chapter deals with the concept of power and ground planes. It provides hints for decoupling and filtering. Information about power-on sequencing and avoiding unwanted loop antenna effects when using a chassis ground plane is also included.

#### **Chapter 5: Layout Guide**

Details on placement and routing rules as well as rules for power and ground planes are described. The instructions of this document should be carried out to ensure a proper design with good performance.

### **Chapter 6: Summary and Design Checklist**

A short checklist describes the most important hardware and layout related details.

**General Design Overview**

## 1 General Design Overview

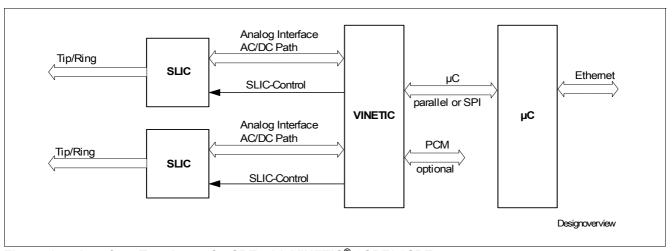

Designing a POTS interface either on a Customer Premises Equipment (CPE) or for other voice communication systems, the Infineon chip set utilizes a single or dual-channel codec/DSP circuit (VINETIC®-2CPE/-1CPE) together with a high-voltage line interface circuit (SLIC-DC).

The VINETIC®-2CPE includes 2 analog line channels which connect to the SLICs, one PCM interface and the Parallel/Serial Control Host Interface to connect to the host controller.

**Figure 1** is a simplified block diagram showing the interface topology of a typical POTS CPE application using Infineons VINETIC®-CPE devices. The VINETIC®-1CPE includes only one analog line channel connected to the SLIC.

Figure 1 Interface Topology of a CPE with VINETIC®-2CPE/-1CPE

One or two analog channel groups can be supported via the Parallel/Serial Control Host Interface to provide packetized voice data (RTP format). This allows easy support of packetized voice applications like VoIP.

The interface between the VINETIC®-2CPE/-1CPE and the SLIC is an interface with separate receive and transmit links (AC/DC) for each channel. Additional lines of the interface control the line status, for example ringing.

## 2 Design Guidelines for VINETIC®-2CPE/-1CPE

This chapter describes the design guidelines for the VINETIC®-2CPE/-1CPE. There are no hardware changes necessary, when the VINETIC®-2CPE/-1CPE is changed from Version 2.1 to Version 2.2. The design guidelines for the SLIC are described in **Chapter 3**. The VINETIC®-2CPE/-1CPE offers the selection of different host interfaces, one PCM interface, up to two analog interfaces, one JTAG interface and eight GPIOs (only with the PG-TQFP-100 package). These interfaces are described in detail in the following chapters.

The parallel/serial host interface is only +3.3 V tolerant. When a controller delivers +5.0 V signals level shifter must be placed in between both devices.

## 2.1 Interface Configurations

Two different packages are available for the VINETIC®-2CPE/-1CPE devices, the PG-TQFP-64 and the PG-TQFP-100 package. The smaller package PG-TQFP-64 only supports the serial host interface (SPI- interface). All other host interface modes are only possible with the PG-TQFP-100 package.

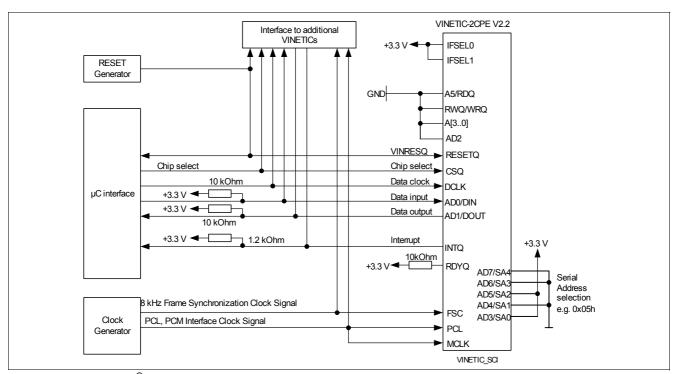

## 2.1.1 Serial Micro Controller Interface Type: SCI + PCM

Figure 2 VINETIC®-2CPE/-1CPE in SCI/SPI Mode

The serial synchronous interface SCI/SPI is selected by connecting the IFSEL pins (IFSEL[1:0]) to the following logic levels:

IFSEL11) = 1

IFSEL0 = 1

It is required that each VINETIC®-2CPE/-1CPE in the PG-TQFP-64 needs a dedicated CSQ line, as the internal address line is  $1F_H$  due to internal pull-ups (SA0..SA4 are not available for PG-TQFP-64 package). The address

<sup>1)</sup>IFSEL[1:0] is not supported with the package PG-TQFP-64 of the VINETIC®-2CPE/-1CPE.

must be transfered in every command. The internal pull-ups are only active in the PG-TQFP-64 package. Address selection in the PG-TQFP-100 package is accessible. In the PG-TQFP-100 package these pull ups are disabled! For example when the address  $05_H$  should be selected, the address selection is set via

AD7/SA4 = 0

AD6/SA3 = 0

AD5/SA2 = 1

AD4/SA1 = 0

AD3/SA0 = 1

The signals can be directly connected to +3.3 V or GND.

The CSQ, DCLK, DIN, and DOUT of several VINETIC®-2CPE/-1CPE devices can be mutually connected to share the same serial host interface when the device is used with the PG-TQFP-100 package. When the device in the PG-TQFP-64 package is used, then only DCLK, DIN and DOUT can be connected.

The interrupt line (INTQ) is active low and is an open drain output. Several VINETIC<sup>®</sup>-2CPE/-1CPE devices can be connected using a pull-up resistor of for example 1.2 k $\Omega$ .

**Figure 2** shows pull-up resistors for DIN, DOUT, INTQ and RDYQ. The DIN and DOUT lines are only driven (high or low) by the VINETIC®-2CPE/-1CPE or the host controller during data transmission. Hence pull-ups prevent floating lines at pins DOUT, DIN, INTQ and RDYQ. The frequency for A4/DCLK can be within a range of 0 kHz and 8.192 MHz.

It must be ensured that the chip select line has high level after reset. If the chip select line can be floating (GPIO of the host controller is input after reset) a pull-up resistor of 2.2 k $\Omega$  must be provided.

Unused data, address and control lines must be connected to GND (see Table 10 Host Interface pins in [1]).

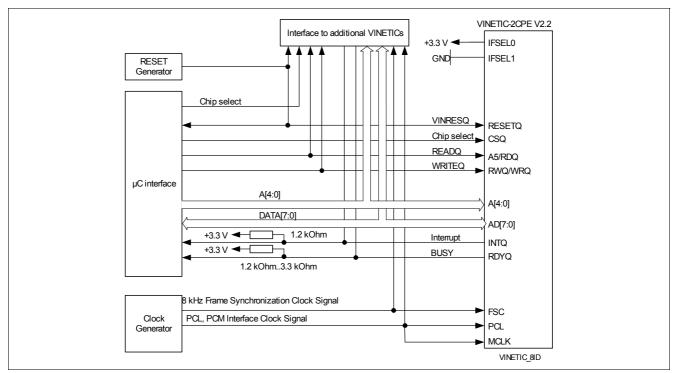

## 2.1.2 Parallel Interface Type: 8-bit INTEL Multiplexed Mode + PCM

The block diagram in **Figure 3** shows how to connect an Intel micro controller interface to the VINETIC®-2CPE/-1CPE. To fulfill the timing of the chip select signal an additional circuitry, as described in **Chapter 2.2**, may be necessary.

Figure 3 Parallel Interface Type: 8-bit INTEL Multiplexed Mode + PCM

The 8-bit INTEL multiplexed mode is selected by connecting the IFSEL pins (IFSEL[1:0]) to the following logic levels:

$IFSEL1^{1} = 0$

IFSEL0 = 0

The interrupt and ready outputs are open-drain. Several VINETIC<sup>®</sup>-2CPE/-1CPE devices can be connected with each other using pull-ups of 1.2 k $\Omega$ .

It must be ensured that the chip select line has high level after reset. If the chip select line can be floating (GPIO of the host controller is input after reset) a pull-up resistor of 1.2 k $\Omega$  must be provided.

Unused data, address and control lines must be connected to GND (see Table 10 Host Interface Pins in [1]).

The default byte ordering in the Intel mode at the data bus is low byte before high byte (little endian).

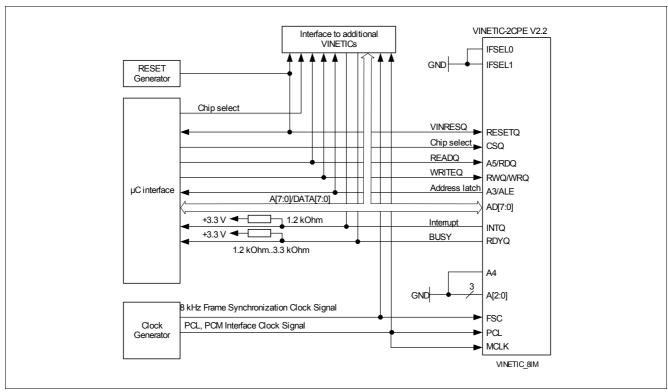

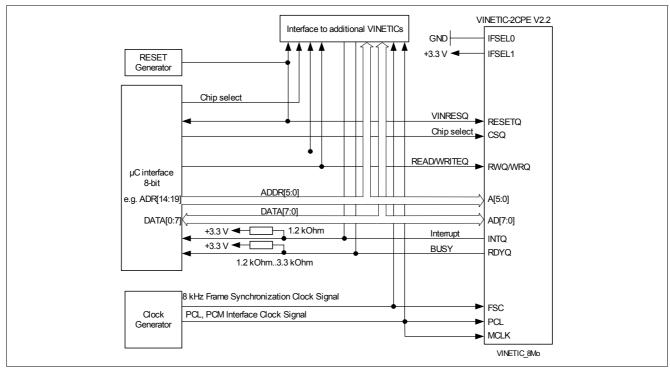

### 2.1.3 Parallel Interface Type: 8-bit INTEL Demultiplexed Mode + PCM

The block diagram in **Figure 4** shows how to connect an Intel micro controller interface to the VINETIC®-2CPE/-1CPE. To fulfill the timing of the chip select signal an additional circuitry, as described in **Chapter 2.2**, may be necessary.

<sup>1)</sup>IFSEL[1:0] is not supported by the package PG-TQFP-64 of the VINETIC®-2CPE/-1CPE.

Figure 4 Parallel Interface Type: 8-bit INTEL Demultiplexed Mode + PCM

The 8-bit INTEL demultiplexed mode is selected by connecting the IFSEL pins (IFSEL[3:0]) to the following logic levels:

$IFSEL1^{1)} = 0$

IFSEL0 = 1

The interrupt and ready outputs are open-drain. Several VINETIC<sup>®</sup>-2CPE/-1CPE devices can be connected using pull-ups of 1.2 k $\Omega$ .

In Intel demultiplexed mode, the VINETIC®-2CPE/-1CPE has five address lines. They may be connected to the addresses A[4:0].

It must be ensured that the chip select line has high level after reset. If the chip select line can be floating (GPIO of the host controller is input after reset) a pull-up resistor of 1.2 k $\Omega$  must be provided.

The default byte ordering in the Intel mode at the data bus is low byte before high byte (little endian).

Figure 5 VINETIC®-2CPE/-1CPE Connected to ADM5120

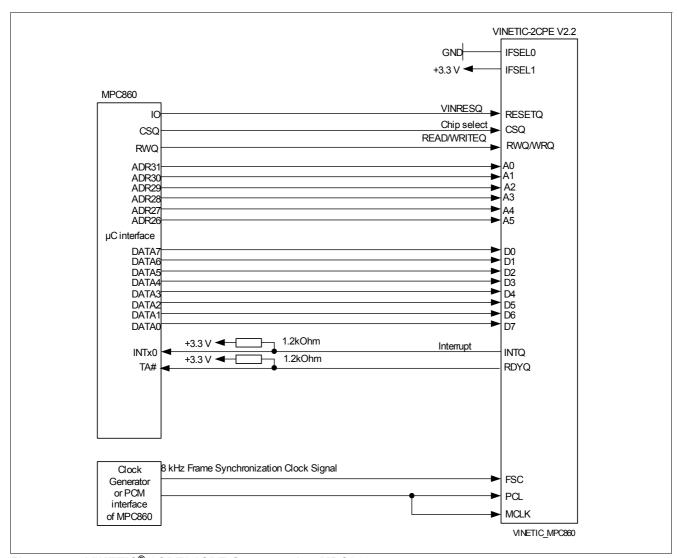

## 2.1.4 Parallel Interface Type: 8-bit MOTOROLA Mode + PCM

Figure 6 Parallel Interface Type: 8-bit MOTOROLA Mode + PCM

The 8-bit MOTOROLA mode is selected by connecting the IFSEL pins (IFSEL[3:0]) to the following logic levels:

IFSEL11) = 1

IFSEL0 = 0

The interrupt and ready outputs are open-drain. Several VINETIC<sup>®</sup>-2CPE/-1CPE devices can be connected using pull-ups of 1.2 k $\Omega$ .

It must be ensured that the chip select line has high level after reset. If the chip select line can be floating (GPIO of the host controller is input after reset) a pull-up resistor of 1.2 k $\Omega$  must be provided.

#### **Data Bus Interface**

The Motorola processors have a different mode in comparison to Intel processors. When a Motorola processor is connected the data lines must be swapped according to **Table 1**. Little endian and big endian are different modes with respect to the sequence of the data bytes.

Little-endian: Low-order byte is stored at the lower address and high-order byte is stored at the higher address.

Big-endian: High-order byte is stored at the lower address and the low-order byte at the higher address.

The VINETIC®-2CPE/-1CPE has an 8-bit interface, although the internal architecture is 16-bit.

The reset behavior for the Motorola Interface is big-endian mode, therefore in the Motorola interface mode the low byte must be transfered before the high byte. The reset behavior for all other interfaces is little-endian.

The default byte ordering in the Motorola mode at the data bus is high byte before low byte (big endian).

<sup>1)</sup>IFSEL[1:0] is not supported by the package PG-TQFP-64 of the VINETIC®-2CPE/-1CPE.

Table 1 Data Bus Connection in 8-bit MOTOROLA Mode

| Motorola Data Pin | VINETIC® Data Pin |

|-------------------|-------------------|

| D0 (MSB)          | AD7 (MSB)         |

| D1                | AD6               |

| D2                | AD5               |

| D3                | AD4               |

| D4                | AD3               |

| D5                | AD2               |

| D6                | AD1               |

| D7 (LSB)          | AD0 (LSB)         |

#### **Address Interface**

The address lines must be swapped in the Motorola mode as well. For example, when the host controller has the address lines ADDR[20:0] then A[0] of VINETIC®-2CPE/-1CPE must be connected to ADDR[20], A[1] is connected to ADDR[19] and accordingly for the remaining address pins.

Figure 7 VINETIC®-2CPE/-1CPE Connected to MPC860

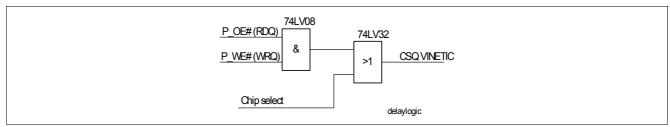

## 2.2 Additional Circuitry for the Chip Select Signal

When the address setup time can not be fulfilled in the INTEL modes by the host controller a circuitry shown in **Figure 8** is recommended to be inserted between the host controller and the VINETIC®-2CPE/-1CPE. The timing is described in figures 14..17 in [1].

Figure 8 Additional Chip Select Logic for some Host Controllers

## 2.3 RDYQ Signal

The VINETIC®-2CPE/-1CPE Version 2.2 RDYQ open-drain output signal, with an external pull-up 1.2...3.3 k $\Omega$  resistor, is recommended to be connected to the Motorola PowerQUICC Family External Bus Interface, Transfer Cycle Termination, Transfer Acknowledge (\*TA) input pin. When the signal is not used, the software must ensure that the access time is always long enough. The VINETIC®-2CPE/-1CPE pulls the signal low after it is finished reading or writing the data. The host controller can then finish the access and disable the chip select signal. This is the indication for the VINETIC®-2CPE/-1CPE to disable the RDYQ signal (high level).

#### 2.4 Reset

The VINETIC®-2CPE/-1CPE has no internal power-on reset function. It has one active low reset input pin called RESETQ. After power-on of the system the RESETQ has to be pulled low for at least 20  $\mu$ s. RESETQ has a spike rejection that will safely suppress spikes with a duration of 2  $\mu$ s.

Before deactivation of the RESETQ signal all power supplies (+1.5 V and +3.3 V) for the VINETIC<sup>®</sup>-2CPE/-1CPE and the clocks (FSC, PCLK and MCLK) have to be stable (see **Chapter 2.5**). No power-on sequence must be performed for the VDD15<sup>1)</sup> and VDD33<sup>2)</sup> supply voltages. It is mandatory to apply the signal voltages after the VDD15 and VDD33 voltages are supplied and stable.

After deactivation of the RESETQ signal (rising edge) the VINETIC® internal PLL starts off synchronization and after the PLL is locked the internal reset routine starts. After completion of the reset routine the host controller access to the VINETIC®-2CPE/-1CPE is possible. The internal reset routine will take approx. 2 ms.

#### 2.5 Clock Distribution

For the VINETIC®-2CPE/-1CPE Version 2.2 or newer the following three clocks must always be provided, regardless of the PCM interface being used or not:

- PCL

- FSC (8 kHz)

- MCLK

The FSC, PCL and MCLK must always be provided, even when the PCM interface is not used. All three clocks have to be synchronous, stable and phase locked (see chapter 4.3.2. in [1]). An internal PLL generates all internal clocks from the MCLK and FSC.

<sup>1)</sup> VDD15, VDD15\_A, VDD15\_B, VDD15\_AB

<sup>2)</sup> VDD33, VDD33\_A, VDD33\_B

The PCL and MCLK can be used from 512 kHz up to 8.192 MHz in steps of 512 kHz. The data rate of the PCM interface is identical to PCL if used in single clocking mode, or half the PCL frequency if used in double clocking mode.

There are two main applications with different ways to generate the clocks for the VINETIC®-2CPE/-1CPE:

- Application with a central distributed clock, for example an application with PCM interface.

- Local clock generation for the VINETIC<sup>®</sup>-2CPE/-1CPE in CPE designs with POTS functions, for example.

## 2.5.1 Application with Distributed Clocks (e.g. via PCM)

In systems like CPE applications with PCM interface there is a central clock distribution unit. The clock distribution can either be done inside a connected device within the application or an external PLL is used to synchronize to a reference clock, for example a modem with ISDN interface. If the reference clock distribution fails or is unstable the clock must be switched to a free running stable clock. This is done in front of the external PLL. The PLL has to generate the stable clock in a way that the PLL unit does not generate a glitch. Such a glitch would increase the jitter (or even lock-out the PLL). The PLL generates all clocks for the VINETIC®-2CPE/-1CPE, that means the FSC, PCL and the MCLK. Sometimes the external PLL has an output to show the status of the PLL. The resynchronization of the external PLL must be done very smoothly to generate synchronization of the VINETIC®. It must be ensured that the PCL and MCLK clocks always have the correct number of clock periods in a FSC frame.

The PCM interface clock PCL must be directly connected to the master clock MCLK.

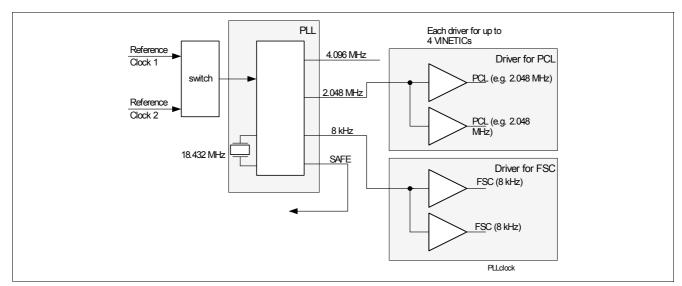

Figure 9 PLL for Generation of PCM Clocks from one of two Reference Clocks

In **Figure 9** for example the external PLL from Cypress CY26049-36 is shown. The reference input frequency of the PLL is 8 kHz and it delivers 8 kHz, 2.048 MHz and 4.096 MHz. It has a status output called SAFE. When the PLL is locked the SAFE output is high. The block switch has three functions: it checks both reference clocks, switches to one of them and divides the clocks to 8 kHz, which is the reference signal for the PLL.

When the SAFE output of the PLL detects an unsynchronous clock signal the VINETIC®-2CPE/-1CPE must be reset so that the clocks become stable again.

### 2.5.2 Local Clock Generation

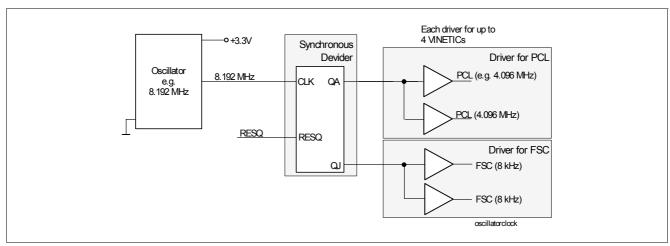

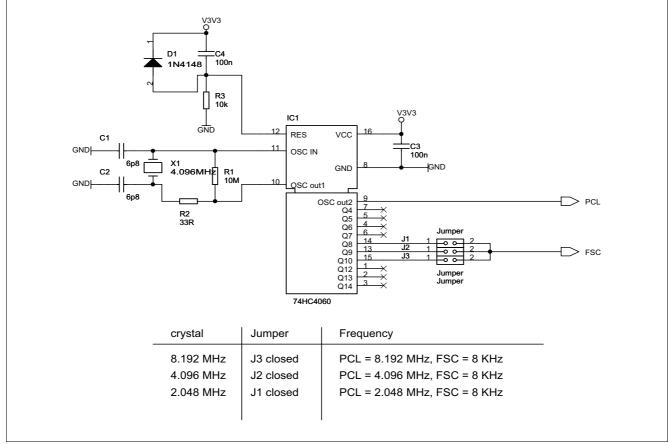

In systems where no reference clock is available (for example a crystal oscillator with a synchronous divider or a crystal with a ripple counter are used), the PCL and the frame signal FSC must be locally generated. Figure 10 shows a clock distribution with a crystal oscillator and a synchronous divider. The maximum frequency of this

generator is 8.192 MHz and the minimum frequency is 2.048 MHz and depends on the circuit used. With ripple counter other frequencies can be realized (see **Figure 11**).

Figure 10 and Figure 11 show only two examples of how to set up a clock distribution block for the VINETIC®-2CPE/-1CPE.

Figure 10 Clock Distribution by Crystal Oscillator and Synchronous Divider

Figure 11 Clock Distribution by Crystal and Ripple Counter

### 2.6 PCM Interface

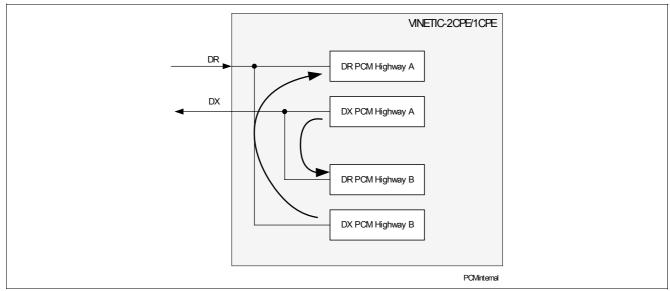

One external PCM highway is available on the VINETIC®-2CPE/-1CPE. A second highway is internally available and cross connected to the external PCM interface (external DX = internal DX1 and it is connected to internal DR2; external DR = internal DR1 and it is connected to internal DX2), see **Figure 12**. In the case of the PCM highway B is used, the pin DR (input of PCM highway) is output of the internal highway B. This feature must be taken into account that the data is corrupt when the same timeslot on the internal highway B and on the external highway is used. The output of an internal driver is only active (push/pull) in the programmed timeslots and in all other timeslots the output driver is in the tristate mode. Therefore, both highway signals DR and DX need a pull-up resistor due to have stable signals in the not used timeslots.

Figure 12 Internal PCM-Highway Connection

The highway is clocked by PCL<sup>1)</sup> (only multiples of 512 kHz are allowed) and FSC (8 kHz) inputs.

The FSC and PCL signals must always be synchronous and in phase. The rising edges of the FSC and the PCL must be aligned, too.

For the timing characteristics of the PCM Interface clocks, about possible PCM data clocks (PCL) and the maximum possible number of time slots that can be assigned to one PCM highway, please refer to the PCM Interface" chapter of [1].

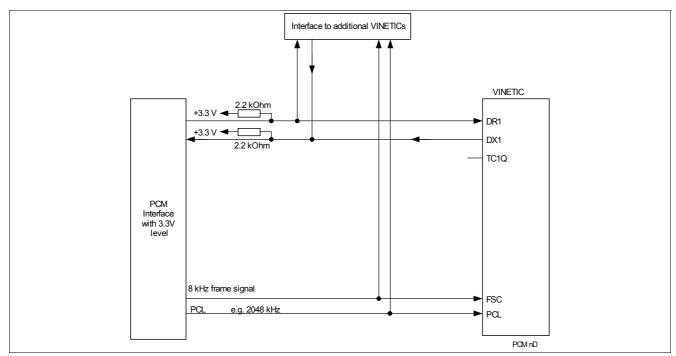

The PCM highway offers a time slot control pin (TC1Q). This pin is intended to control an external buffer device when a PCM highway needs to be multiplexed. The TC1Q pin is open drain. When the pin is used to control external buffer devices, a pull-up resistor needs to be used (e.g. of  $2.2 \text{ k}\Omega$ ).

<sup>1)</sup> Valid PCL clock rates are  $f = n \times 512 \text{ kHz}$  ( $1 \le n \le 16$ ).

Figure 13 PCM Highway and no Driver at +3.3 V PCM Highway

The PCM highway output DX1 should also be tied high to +3.3 V using a 2.2 k $\Omega$  pull-up resistor. The PCM highway input DR1 should also be tied high to +3.3 V using 2.2 k $\Omega$  pull-up resistors.

Since the DR1 and DX1 are I/O pins to enable the cross-connection of the 2 internal PCM highways the DR1 and DX1 pins, if not used, should be connected via a pull-down-resistor (for example 1  $k\Omega$ ) to GND to make sure that nothing is floating. When a transmit timeslot of the PCM highway B (DX2) is enabled, the data is output on the input pin DR1. In this case the system must be set this timeslot to tristate on the external PCM highway.

Note: Do not leave these pins floating.

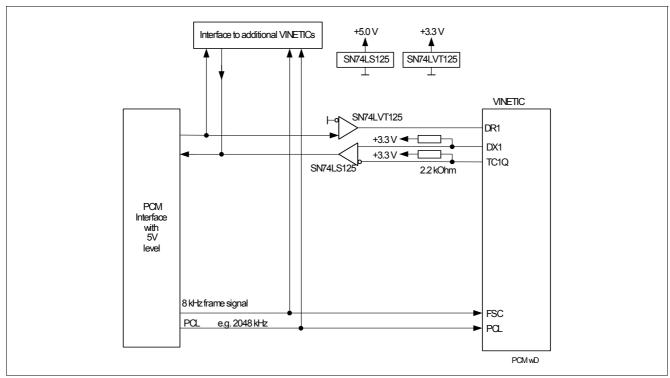

The VINETIC®-2CPE/-1CPE has +3.3 V tolerant IOs only. As many PCM highways are +5 V systems in such a case a driver has to be placed as a level shifter between both "worlds". The driver in the receive direction is of a different type than in transmit direction, due to the needed power supplies. In the direction from VINETIC®-2CPE/-1CPE to the PCM highway a SN74LS125 with +5 V power supply and in the direction from PCM highway to VINETIC®-2CPE/-1CPE a SN74LVT125 with +3.3 V power supply can be used.

Figure 14 PCM Interface with Driver at +5 V PCM Highway

### 2.7 JTAG

The VINETIC®-2CPE/-1CPE offers a JTAG Interface for Boundary Scan support.

The JTAG Interface comprises the pins TRSTQ, TDI, TDO, TMS, and TCK. These pins must be connected to a defined potential via 10 k $\Omega$  resistor (pull-up/pull-down) when the JTAG Interface is used.

The TRSTQ needs a reset signal (active low) before the JTAG interface can be used. The boundary scan test equipment must support the JTAG reset signal.

When the JTAG Interface is not used, all JTAG related input pins must be tied to GND (TMS, TCK, TDI and TRSTQ). The JTAG output TDO must be left open when JTAG is not used.

## 2.8 GPIOs

The VINETIC®-2CPE/-1CPE in the PG-TQFP-100 package offers digital general purpose GPIO pins. If a GPIO pin is not used, it should be connected to ground via a 10 k $\Omega$  resistor. In order to ensure that it is never configured as an output, this pin can directly be connected to ground.

## 2.9 Analog Interfaces

The VINETIC®-2CPE/-1CPE has up to 2 analog interfaces, each one including an AC loop, a DC loop and a control interface. The AC path is used for the typical Codec functionalities: voice AD and DA conversion, impedance matching, gain adjustment, hybrid and ringing.

The DC loop provides the DC Feeding (48 V open loop voltage).

The analog interface has two channel specific input pins for line testing and two control lines with ternary logic to set the mode of the SLIC.

## 2.9.1 Signal Interfaces

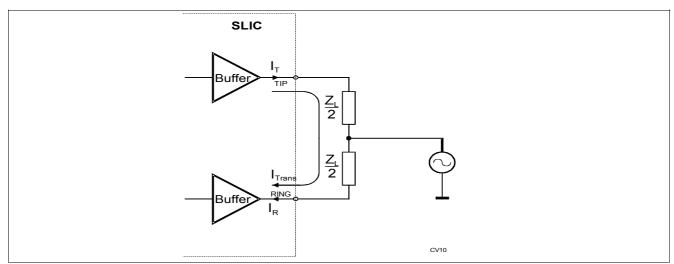

The AC and DC paths include all types of signals like voice, ringing and feeding, and also the howler tone. In receive direction, the voltage information is transferred via the differential interface DCP/DCN and ACP/ACN, whereas in transmit direction the transversal current IT carries the line current information. An RC network serves for current/voltage conversion and AC/DC separation.

### 2.9.2 Control Interfaces

The various SLIC operating modes are controlled by the ternary interfaces C1 and C2.

## 3 Design Guidelines for SLICs

This chapter describes the external components at SLIC-DC. For the circuitry of the DC/DC converter please refer to [3].

### 3.1 VINETIC®-SLIC Interface

## 3.1.1 Signal Interfaces

AC and DC paths are formed by feeding voltages to the line and measuring line currents. In receive direction, the voltage information is transferred via the differential interface pins DCP/DCN and ACP/ACN, whereas in transmit direction pin IT contains the line current information. An RC network serves for current/voltage conversion and AC/DC separation.

## 3.1.2 Influence of External Components

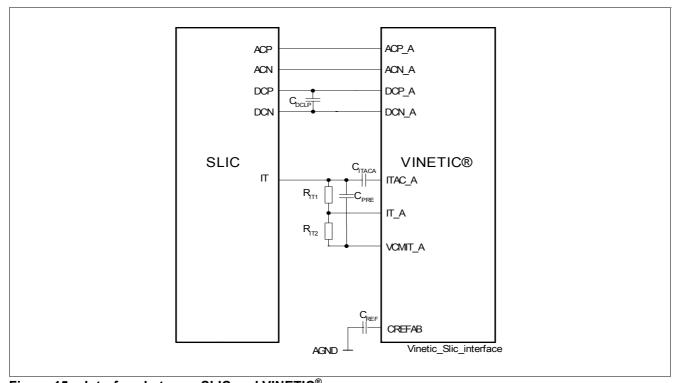

Figure 15 shows the 6 external components of the VINETIC®-SLIC interface.

There are 6 external components between VINETIC® and SLIC. They have an influence on the CRAM coefficients calculated by the coefficient calculation program VINETICOS. The SLIC scales down the transversal line current by a factor of 50 whereas the resistor at the pin IT transforms it into a voltage. The SLIC pin IT carries the scaled current reflected by the SLIC. The VINETIC® measures the voltage at the input pin IT, and the feedback voltage is transferred back to the SLIC through the DCP-DCN pins. A filter capacitor is designed differentially between DCP and DCN for optimizing the noise performance.

## 3.1.2.1 External Components between SLIC and VINETIC®

Figure 15 Interface between SLIC and VINETIC®

#### **CONFIDENTIAL**

**Design Guidelines for SLICs**

The recommended values of these components are:

$C_{\text{DCLP}}$  = 100 nF, 6.3 V, 10%

$C_{\rm ITAC}$  = 1  $\mu$ F, 10 V, 10 %

$C_{\mathsf{REF}}$  = 68 nF, 10 V, 20 %

$C_{\mathsf{PRE}}$  = 4.7 nF,10 V, 5 %

$R_{\rm IT1}$  = 499  $\Omega$ , 1 %

$R_{\rm IT2}$  = 499  $\Omega$ , 1 %

The SLIC senses the transversal line current, scales it down and outputs it at pin IT.

The relationship between the scaled current  $I_{\rm IT}$  and the actual line currents in Tip ( $I_{\rm T}$ ) and Ring ( $I_{\rm R}$ ) line is given by:

$$I_{\rm IT} = (I_{\rm T} + I_{\rm R})/100 = I_{\rm TRANS} / 50$$

(1)

$$I_{\mathsf{TRANS}} = (I_{\mathsf{T}} + I_{\mathsf{R}})/2 \tag{2}$$

Figure 16 Transversal Currents

$I_{\rm IT}$  represents the transversal line current.

The pin IT of SLIC-DC is a current output. The resistors  $R_{\rm IT1}$  and  $R_{\rm IT2}$  are used to convert this current into a voltage. The potential  $V_{\rm IT}$  at the IT pin of the VINETIC® is described as:

$$V_{\rm IT} = VCMITx - I_{\rm IT} * R_{\rm IT2} = VCMITx - (I_{\rm T} + I_{\rm R})/100 * R_{\rm IT2}$$

(3)

VCMITx stands for VCMITA or VCMITB and is a virtual ground supplied by the VINETIC® (typically 0.7 V).

The voltage at  $V_{\rm IT}$  input of the VINETIC<sup>®</sup> represents the transversal current on the line. This value is used to control the DC feeding loop.

The capacitor in front of the ITAC input separates the AC from the DC component. The voltage at ITAC goes into the AC control loop.

$$V_{\rm ITAC} = I_{\rm IT} * (R_{\rm IT1} + R_{\rm IT2}) = (I_{\rm T} + I_{\rm R})/100 * (R_{\rm IT1} + R_{\rm IT2})$$

(4)

If  $R_{\rm IT1}$  and  $R_{\rm IT2}$  deviate from the default values ( $R_{\rm IT1}$  = 499  $\Omega$ ,  $R_{\rm IT2}$  = 499  $\Omega$ ), all programmed voice levels in transmit direction would deviate from the calculated ones. Return loss and transhybrid loss will also be influenced if  $R_{\rm IT1}$  and  $R_{\rm IT2}$  deviate from the default values.

As VINETICOS calculates with  $R_{\rm IT1}$  = 499  $\Omega$  and  $R_{\rm IT2}$  = 499  $\Omega$ , it is definitely required to use the recommended values and **not to change** these values. Recommend tolerance for  $R_{\rm IT1}$  and  $R_{\rm IT2}$  is 1%.

**CONFIDENTIAL**

**Design Guidelines for SLICs**

## 3.1.2.2 C<sub>ITAC</sub>

Recommended value:  $1 \mu F$

This capacitor is in series to the ITAC input pin of the VINETIC<sup>®</sup>. It separates the AC from the DC component of transversal current  $I_{\text{TRANS}}$ .  $C_{\text{ITAC}}$  and the input impedance of the AC input filter build a highpass filter with a cut-off frequency of roughly 10 Hz.

As VINETICOS calculates the AC coefficients based on a value of 1  $\mu$ F, it is recommended not to change this value.

## 3.1.2.3 C<sub>PRE</sub>

Recommended Value: 4.7 nF

This capacitor is in parallel to the resistors  $R_{\rm IT1}$  and  $R_{\rm IT2}$  and builds a lowpass filter with a cut-off frequency of 33.8 kHz. The lowpass reduces the out of band noise from the SLIC and ensures stability to the impedance loops.

### 3.1.2.4 C<sub>RFF</sub>

Recommended value: 68 nF

This capacitor is used for filtering the internal bandgap reference voltage.

The minimum value used should be 68 nF.

## 3.1.2.5 C<sub>DCLP</sub>

Recommended value: 100 nF

This external noise filter capacitor is placed in the DCP/DCN lines. It must be placed with very short traces to the SLIC.

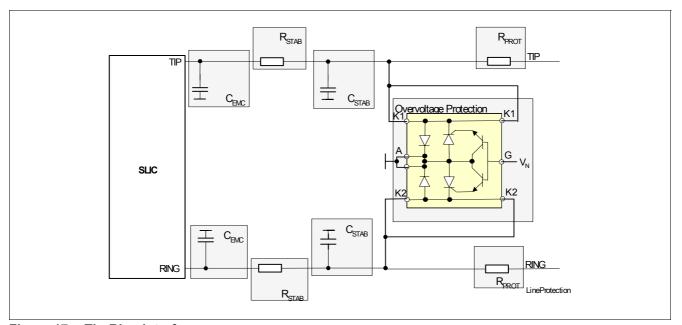

## 3.2 Tip-Ring Interface: $C_{STAB}$ , $R_{STAB}$ , $R_{PROT}$ and $C_{EMC}$

Recommended values:

$C_{\mathsf{STAB}}$ : 15 nF

$R_{\rm STAB}$ : 20  $\Omega$  for SLIC-DC and 30  $\Omega$  for SLIC-E

$R_{\text{PROT}}$ : 20  $\Omega$  (value depending on protection scheme) Optional - recommended values in noisy environment:

$C_{\mathsf{EMC}}$ : 100 pF

Figure 17 Tip-Ring Interface

## 3.2.1 C<sub>STAB</sub>

The proposed capacitors help to ensure stability for all line conditions and also contribute to EMC immunity. 15 nF/100 V caps are recommended. Increasing the value up to 25 nF should be uncritical. VINETICOS also calculates and plots the input impedance up to 1 MHz. There will be an error message, if the real part of the input impedance is negative. This is a criterion for the stability of the system. For negative values the stability cannot be guaranteed for all line conditions (for example a short cut). This error message must not be ignored.

Increasing  $C_{\mathsf{STAB}}$  results in better out of band noise performance and higher stability margin for complex AC impedances (for example impedance for Germany). It also causes worse stability for pure resistive AC impedances.

A changed value for  $C_{\rm STAB}$  has to be taken into account when calculating coefficients with VINETICOS. The SLIC circuitry definition of VINETICOS allows changing of  $C_{\rm STAB}$  value.

The maximum stress for the capacitor occurs when the over-voltage protector (thyristor) fires. Because the capacitor in the stability network is connected to GND by the very low impedance track over the thyristor, the capacitor will discharge to GND.

## 3.2.2 R<sub>STAB</sub>

Recommended value: 20  $\Omega$  for SLIC-DC Recommended value: 30  $\Omega$  for SLIC-E

The value for  $R_{\text{STAB}}$  can be increased up to 40  $\Omega$ . A minimum value of 20  $\Omega$  (30  $\Omega$  for SLIC-E) is required to guarantee system stability. The actual value for  $R_{\text{STAB}}$  has to be taken into account when calculating coefficients with VINETICOS. The SLIC circuitry definition of VINETICOS allows changing of  $R_{\text{STAB}}$  value.

Changing  $R_{\rm STAB}$  also influences the pole frequency of the RC filter ( $R_{\rm STAB}$ ,  $C_{\rm STAB}$ ).

If  $R_{\rm STAB}$  is increased, the out of band noise performance and the stability for pure resistive AC impedances will be improved. Increasing  $R_{\rm STAB}$  also means to increase the voltage drop caused by line feeding. This might be an issue in power critical applications.

The tolerance matching of the two  $R_{\rm STAB}$  resistors in Tip and Ring line also influences the longitudinal balance performance.

## $R_{PROT}$

Recommended value: 20  $\Omega$  (actual value depending on protection scheme)

The value for  $R_{\text{PROT}}$  can be changed up to 50  $\Omega$ . This value has to be taken into account when calculating coefficients with VINETICOS. The SLIC circuitry definition of VINETICOS allows changing of  $R_{\text{PROT}}$  value.

The function of  $R_{\mathsf{PROT}}$  is to limit the current into the protection device in case of a foreign voltage contact (lightning, power contact).  $R_{\mathsf{PROT}}$  and  $C_{\mathsf{STAB}}$  also form a lowpass filter which helps to improve EMC behavior. By changing  $R_{\mathsf{PROT}}$  the characteristic of this filter is changed, too.

$R_{\mathsf{PROT}}$  also influences the stability of the impedance matching loop but this can be compensated by changing  $R_{\mathsf{STAB}}$ .

The pins TIP and RING of SLIC-DC has internal 10  $\Omega$ . This value has to be taken into account when calculating the value of R<sub>PROT</sub>. VINETICOS calculates with this internal resistor value of 10  $\Omega$ .

To increase  $R_{\mathsf{PROT}}$  means to decrease the current in case of a foreign voltage contact and to increase the voltage drop caused by the line feeding (might be an issue in power critical applications).  $R_{\mathsf{PROT}}$  should be rated for lightning surge currents and also should act as a fuseable resistor in order to open the line in case of a power contact.

The tolerance matching of the two  $R_{\mathsf{PROT}}$  resistors in Tip and Ring line also influences the longitudinal balance performance.

Note: In order to be able and flexible to meet worldwide AC impedance requirements it is recommended to have  $R_{STAB} + R_{PROT} > 50 \ \Omega$  for SLIC-E, T-SLIC-E and  $R_{STAB} + R_{PROT} > 40 \ \Omega$  for SLIC-DC.

## 3.2.4 Capacitors for Enhanced EMC Requirements C<sub>EMC</sub>

To fulfill the EMC requirements in noisy environments, two additional 100pF/100V capacitors are recommended at the TIP and RING pins of the SLIC. These capacitors are optional and must be placed directly at the pins with a short connection to GND.

Only in case of very dense placement of RSTAB and CSTAB and short connection to the pins and to GND the CEMC might not be necessary.

### 3.3 Additional Protection Devices at the Line

In general, gate-triggered devices are recommended for overvoltage protection of the SLIC. These gate-triggered thyristors are "programmable". Gate programmable devices track the substrate voltage of the SLIC. By connecting the gates of these battery tracking devices to the supply rails, overvoltages are limited to the supply rails of the SLIC.

Capacitors must be placed on the gate pin of the thyristor to provide the current for the thyristor to trigger when the fault condition on the line appears. These thyristors are switching very fast (a few nanoseconds). The current required for this fast thyristor switching must be provided by the gate capacitors.

Note: Suitable protection circuits for SLIC-DC V1.2 can be found in detail in [5]. Suitable protection circuits for the SLIC-E can be found in [6].

### 3.4 External Circuitry for GR-909 Support

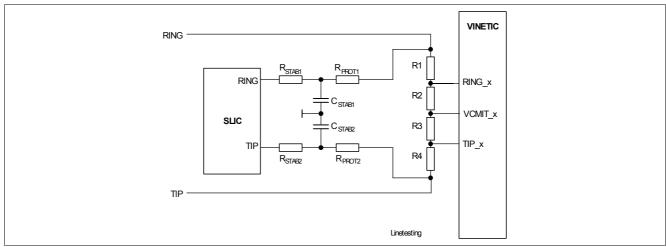

A resistive voltage divider at the Tip and Ring line is necessary to support GR-909 measurements. The requirements for the resistors depend on the foreign line peak voltage and the allowed leakage current. To calculate the correct resistor values, the analog inputs of the VINETIC® only allows a voltage between VCMITx ±0.7 V. The resistors¹) must be able to withstand the peak power and voltage during overvoltage protection mode.

<sup>1)</sup> These resistors are only required if GR-909 measurements need to be supported. In case no GR-909 support is required, these resistors are not needed.

Derived from overvoltage and longitudinal balance standards, they require both high power rating and good matching ( $\pm$  1.0 % or better, depending on application).

The line testing network is typically connected to the TIP, RING and VCMITA or VCMITB respectively of the VINETIC®-2CPE/-1CPE (see Figure 18).

Figure 18 Line Testing Resistors at RING/TIP

Recommended resistor values are:

$R1 = 1.5 M\Omega$

$R2 = 3.3 \text{ k}\Omega$

$R3 = 3.3 \text{ k}\Omega$

$R4 = 1.5 M\Omega$

## 4 Power Supply and Grounding

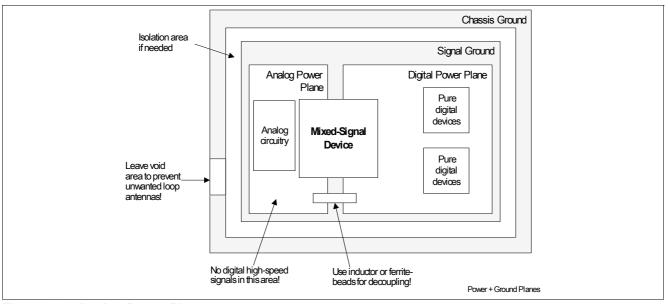

### 4.1 General Overview of Power and Ground Planes

Usually four different supply areas are distinguished: the analog and the digital power planes and the signal ground and chassis ground planes.

General rules for power and ground planes are:

- Provide sufficient power and ground planes to have low-impedance current paths.

- Avoid power distribution using traces. This will add additional impedance, which can lead to a significant voltage drop.

- Split power planes to minimize the number of PCB layers.

- Avoid slots in the ground plane. This is fundamental for areas where high-frequency or sensitive analog signals

are crossing over.

- Route high-speed signals above a continuous, unsplitted ground plane.

- The ground of the over-voltage protector should have a very low ohmic connection to the ground of the SLIC device.

- In two layer designs the ground planes at both sides must be connected with many vias.

## 4.1.1 Analog Power Plane

In mixed signal designs, it is essential to eliminate signal crosstalk and digital noise disturbers in the analog section of the PCB.

The analog power planes for the VINETIC®/SLIC section extend from the SLIC to the VINETIC®-2CPE/-1CPE analog Interface, including the complete circuitry between VINETIC®-2CPE/-1CPE and SLIC.

The following specific recommendations apply to the design and layout of the analog power planes with the VINETIC®-2CPE/-1CPE Chip Set Family:

- Divide the +3.3 V and the +1.5 V power plane into a minimum of two sections (as shown in Figure 20) to separate the digital (VDD15, VDD33) from the analog power supply (VDD15A, VDD15B, VDD15AB, VDD33AB).

- When dividing power planes, it is possible to save additional layers. Simply create cut-out regions in the dedicated power supply layer to form several copper areas.

- Join the analog and digital sections at multiple points by 0 Ω resistors, ferrite-beads or inductors, depending on the need for additional filtering.

- It is acceptable to supply all VINETIC®-2CPE/-1CPE and SLIC devices from one analog power plane. This

analog plane can be multiple times connected to the digital power plane. Each junction must provide a lowimpedance connection and additional filtering if necessary. It is also possible to have a small analog power

plane for each device.

- Place high-frequency bypass capacitors (100 nF, 10 nF) near the supply pins of the devices. The Reference Schematics show the minimum decoupling requirements of each device.

- Place bulk capacitors (10 μF and higher) close to the appropriate devices to reduce distortions from transients.

Choosing low ESR types (at analog power supplies).

- The battery power supply  $V_S$  of SLIC-DC can be routed in traces width 15 mil (1 mil = 0.0254 mm). This power supply does not need a plane. It is recommended to filter the supply by a 100 nF capacitor.

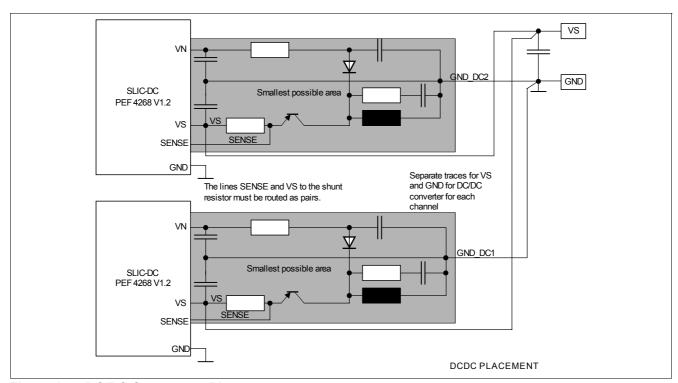

- In designs with SLIC-DC the power supply signals V<sub>S</sub> and ground of the DC/DC high current ground need separate traces for each channel. Both signals are connected at a star point placed near the power supply input at the bulk capacitor. No planes are necessary for high current ground and V<sub>S</sub> (Figure 19).

Figure 19 DC/DC Component Placement

Figure 20 Analog Power Plane

## 4.1.2 Digital Power Plane

The digital power plane spans the area from the board edges, where the backplane connectors are located, to the digital parts of the VINETIC®-2CPE/-1CPE. The digital power plane supplies all digital parts of the VINETIC®-2CPE/-1CPE Chip Set Family (VDD15, VDD33). The analog parts should be decoupled from the digital power plane.

Some recommendations for the digital power plane include:

• For good capacitive coupling and resulting reduction in high-frequency voltage ripple, have a signal ground plane in a layer adjacent to a digital supply plane.

- When dividing the digital power plane, it is not necessary to add layers. Create cut-out regions in the dedicated power supply layer to form several copper areas.

- Place high-frequency bypass capacitors (100 nF, 10 nF) near the supply pins of the devices. The Reference Schematics show the minimum decoupling requirements.

- Place bulk capacitors (10 μF and higher) close to the appropriate devices. Choosing low ESR types provides reduced distortions.

## 4.1.3 Signal Ground Plane

It is recommended that the signal ground is a continuous, unsplitted plane. Under the SLIC device footprint and directly under the protection elements this plane might be omitted.

Note: The most important rule is to use a continuous, unslotted signal ground plane in the high-speed digital area.

Use at least one dedicated layer as a ground plane. This also improves signal integrity as no impedance changes for signal lines will occur.

All devices must be connected to one single GND. It is not recommended to split this into digital and analog grounds. If the GND plane is split for some other reason, it is important that the VINETIC®-2CPE/-1CPE's GND pins be connected to a large GND area, which itself is connected to GND by a low impedance path to GND, in order to avoid ground bouncing. Additionally no high-speed digital signals must cross this slot, as this increases EMI. The GND of the VINETIC®-2CPE/-1CPE's host controller interface must be connected as a large area to avoid ground bouncing.

#### 4.1.4 Chassis Ground Plane

A chassis ground plane is used for EMC requirements and for protection purposes. Place this plane directly next to the signal ground plane to ensure an excellent capacitive coupling between both planes. An external chassis should be connected to the plane in multiple places.

The chassis ground plane extends from the board edges to the protection part of the SLICs. The complete board perimeter should be included in this chassis ground plane.

## 4.1.5 Avoiding Loop Antenna Effect

When laying out ground planes, it is vitally important to avoid loop antenna effects. A loop antenna could easily catch some unwanted noise and impair the complete system performance.

- Implement all ground planes as solid rectangular areas.

- Avoid creating loops with ground planes around other ground planes. The only exception is the chassis ground plane as it must run around the board perimeter.

By layout, ensure that the chassis ground loop is left at one point. The cut-out of the left gap must be large enough to avoid loop antenna effect.

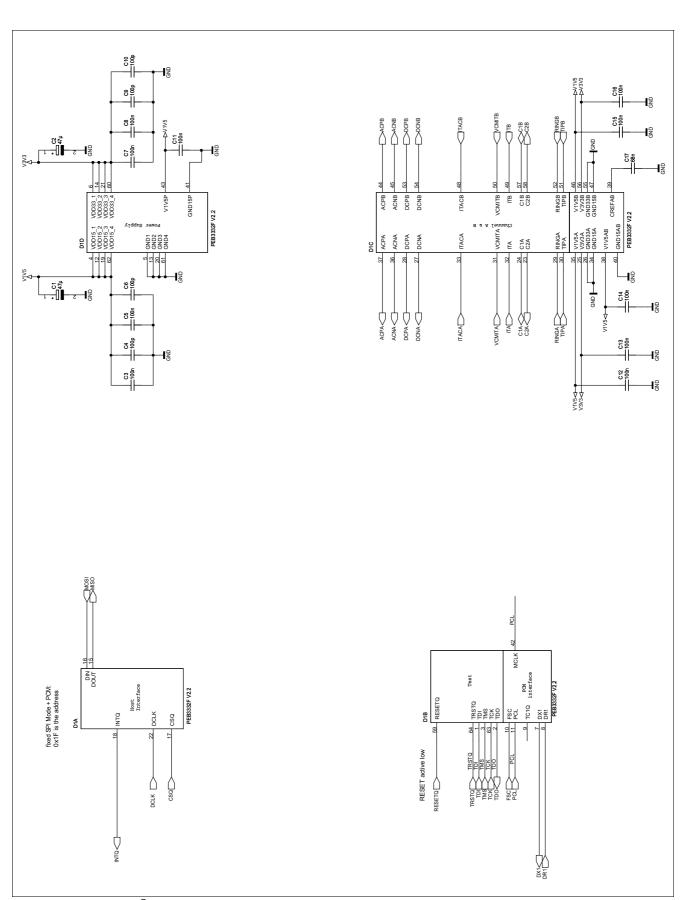

## 4.2 VINETIC® Supply

The VINETIC®-2CPE/-1CPE chip requires two supply voltages: +3.3 V and +1.5 V. There is no power-on sequence necessary. A simultaneous ramp-up of the two VINETIC®-2CPE/-1CPE supply voltages is allowed. The tolerance of both supply voltages is  $\pm 5\%$ .

The minimum capacitance value for blocking is 10 μF (47 μF recommended) in sum at all power supply pins.

The following supply voltages are used to supply digital sections in the VINETIC®-2CPE/-1CPE:

- VDD33: Digital Supply I/O Pads (+3.3 V)

- VDD15: Power Supply digital parts (+1.5 V)

The following supply voltages are used to supply analog sections in the VINETIC®-2CPE/-1CPE:

#### CONFIDENTIAL

**Power Supply and Grounding**

- VDD33xx: Analog Supply Channel xx (+3.3 V)

- VDD15xx: Analog Supply Channel xx (+1.5 V)

- VDD33x: Analog Supply Channel x (+3.3 v)

- VDD15x: Analog Supply Channel x (+1.5 V)

The analog supply voltages must be kept separated and connected at a central point in the design. It is not required to locally generate the analog supply voltages for the VINETIC®-2CPE/-1CPE. The +3.3 V analog supply of the VINETIC®-2CPE/-1CPE can be connected to the +3.3 V digital supply via LC-filters or ferrite-beads (140  $\Omega$ @100 MHz, 0.55  $\Omega$ DC, 200 mA) or via 0  $\Omega$ -resistors, if possible.

The power supply pins of the PLL of the VINETIC®-2CPE/-1CPE are described in Chapter 4.4.2.

For the maximum power consumption of the VINETIC®-2CPE/-1CPE, see [1].

## 4.3 SLIC Supply

### 4.3.1 SLIC-DC

The SLIC-DC device generates all the required high voltages from a single +9 V up to +40 V DC power supply. A 100 nF ceramic capacitor must be placed directly at the VS pin.

A good blocking of the supply voltage VS is required in order to maintain a minimum voltage of VS = 9 V for SLIC-DC V1.2 at all operating conditions. The highest power consumption appears during ring trip. In some cases, the fast ring trip feature of the VINETIC®-2CPE has to be used.

### 4.3.2 SLIC-E

The SLIC device requires up to four supply voltages:  $V_{DD}$ ,  $V_{BATL}$ ,  $V_{BATH}$  and  $V_{HR}$ . The SLIC-E offers the possibility to be operated at two different negative battery supply voltages and utilize an auxiliary positive supply for internal ringing.

The power rail  $V_{DD}$  can be +3.3 V or +5.0 V. The VDD supply of the SLIC-E is an analog supply voltage and must be separated from the digital supply on the board. This  $V_{DD}$  analog voltage must be connected to the analog power supply rail of the board. A 100 nF ceramic capacitor must be provided at the VDD pin.

If  $V_{BATL}$  is not used, the  $V_{BATL}$  pin of the SLIC must be connected to the  $V_{BATH}$  pin directly at the SLIC device.

If V<sub>HR</sub> is used, the specified limits for the total supply voltage must not be exceeded.

In order to guarantee the condition  $V_{BATL} < V_{BATL}$  under all operation conditions, fast rectifier diodes (fast or ultra fast type) must be inserted between  $V_{BATL}$  and  $V_{BATL}$ . Please refer to **Chapter 4.4.3** and to the reference schematics for detailed information.

## 4.4 Supply Filtering

## 4.4.1 Decoupling of the VINETIC®-2CPE/-1CPE Supply Voltages

For the core supply pins (VDD15) of the VINETIC<sup>®</sup>-2CPE/-1CPE, four 100 nF ceramic capacitors and one large 47  $\mu$ F ceramic capacitor are recommended.

For the digital interface supply pins (VDD33) of the VINETIC<sup>®</sup>-2CPE/-1CPE, four 100 nF ceramic capacitors and one large 47  $\mu$ F ceramic capacitor are recommended.

For the analog +1.5 V supply pins (VDD15x, VDD15xx), a 100 nF decoupling capacitor is required on each supply pin (three capacitors). For the analog +3.3 V supply pins (VDD33x, VDD33xx), a 100 nF decoupling capacitor is required on each supply pin (two capacitors).

All blocking capacitors of the not used channel specific pins can be removed, when the VINETIC®-1CPE is used.

## 4.4.2 PLL Supply Voltage

Special treatment is required for the PLL supply voltage, as the PLL is sensitive to ripple peaks and to ground bouncing effects. The pins VDDP and GNDP must be connected with short lines directly to the planes. A blocking capacitor of 100 nF must be placed directly at the pins to filter high frequency power supply noise and the ground bouncing. For the value of the decoupling capacitor please refer to the VINETIC®-2CPE/-1CPE reference schematics.

## 4.4.3 Decoupling of the SLIC-E Supply Voltages

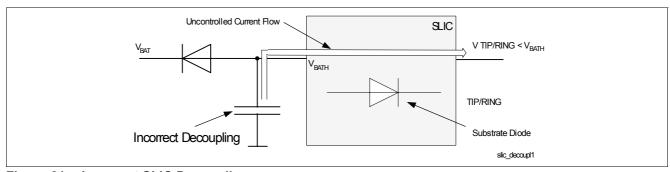

$V_{BATH}$ , the substrate potential of SLIC-E, must always be the most negative pin. Otherwise, any other pin below  $V_{BATH}$  would possibly excite parasitic elements. As a consequence dangerous parasitic substrate currents can occur. The requirement  $V_{BATH}$  pin the most negative potential of the SLIC-E cannot be guaranteed in some situations (for example powering-up, overvoltages at the line). Thus the use of protection diodes in the power supply rails as shown in **Figure 22** and **Figure 23** is strongly recommended.

If a voltage on the Tip/Ring line appears that is more negative than the most negative SLIC supply voltage potential, the internal substrate diodes, which are normally reverse biased, start to conduct. If a decoupling capacitor is placed directly at the V<sub>BATH</sub> pins of the SLIC device this capacitor is able to discharge through the SLIC onto the Tip/Ring line. The current flow from the capacitor through the SLIC towards the Tip/Ring line is uncontrolled. This situation is shown in **Figure 21**. Thus, do not place a decoupling capacitor directly on the SLIC battery power pins.

Figure 21 Incorrect SLIC Decoupling

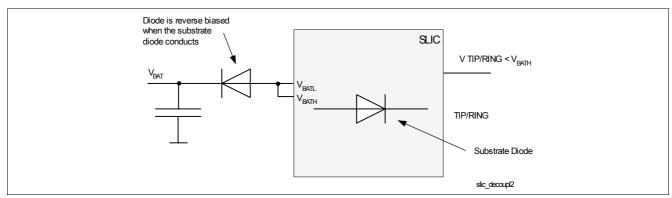

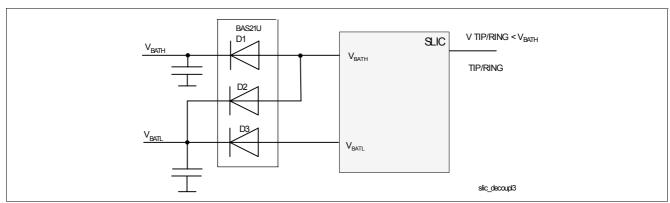

**Figure 22** and **Figure 23** show the correct SLIC decoupling. Fore more information please refer to the reference schematics in **Chapter 7**.

On DC/DC converters, large capacitors are placed on the output to reduce the switching noise. These large capacitors also should not be discharged into the SLIC. For this reason, series diodes are required between the power supply pins of the SLIC and the output of the DC/DC converters.

These external diodes must be provided for every single SLIC device.

Figure 22 Correct SLIC Decoupling

Figure 23 Correct SLIC Decoupling for two Battery Supplies

The diode D1 in the  $V_{BATH}$  power rail blocks any substrate current resulting from line potentials below  $V_{BATH}$ , whereas the other two diodes D2 and D3 (**Figure 23**) ensure that the SLIC pins is guaranteed the requirement  $V_{BATH}$ , regardless of the actual external supply voltage situation. Thus any critical behavior with respect to power-on sequence or missing supply voltages can be avoided. The SLIC power supply diodes must be fast or ultra fast types. The relevant diode parameter is the "reverse recovery time". Diodes with reverse recovery times of less than 50 ns are suitable.

**Layout Guide**

## 5 Layout Guide

This chapter serves as a guideline for the placing and routing processes during layouting. It gives an overview of recommended layer stacks and contains information about how to arrange components in order to guarantee a reliable operation of the system. Furthermore detailed information about the routing of signal paths in order to achieve best system performance is provided.

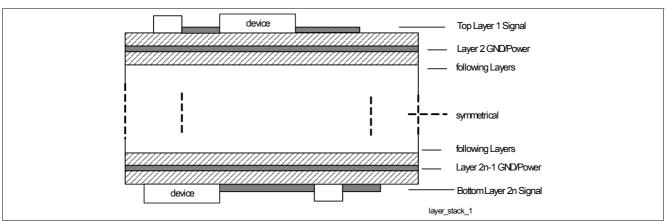

### 5.1 Layer Stack

It is very important to have a GND or other power layer underneath the surface layers (top and bottom).

It is good practice to have max. two adjacent signal layers<sup>1)</sup>, which are then followed by a GND or power supply layer. For the top and bottom layers it is recommended to use only one signal layer which is followed by a GND or power supply layer.

The next picture shows the layer stack structure:

Figure 24 Layer Stack Setup

For TQFP-packages a 4-layer PCB is recommended, although a 2-layer board can be realized.

The number of layers has to be even and a symmetrical layer stack is recommended for reliable PCB production. An example for a 4-layer stack:

- · Signal/GND layer-1 at the component side

- GND

- Power

- · Signal/GND layer-2 at the solder side

## 5.2 Layout Recommendations

In all figures of this chapter the analog channel specific decoupling capacitors are shown, whereas all decoupling capacitors for the digital power supplies are not shown.

### 5.2.1 Placement

The following placement hints are described with component references. These references are shown in the schematics in the Appendix.

Place all components between SLIC and VINETIC<sup>®</sup> (with the exception of C<sub>DCLP</sub>) close to the VINETIC<sup>®</sup>.

<sup>1)</sup> If signal layers are adjacent it is strictly recommended to do routing in orthogonal directions, that means one signal layer has tracks mostly in x-directions, the other in y-direction. If parallel routing can not be avoided the distance has to be as far as possible.

CONFIDENTIAL Layout Guide

- The VINETIC®-2CPE/-1CPE and SLIC have to be placed as close as possible to each other.

- Place decoupling capacitors as close as possible to the supply pin of the device package and associated ground pin.

- Place VINETIC<sup>®</sup> and SLIC device in such a way that tracks ACP, ACN, DCP, DCN, IT, ITAC are as short as possible.

The recommendations at the line side are:

- The resistors R1\_x, R3\_x (R<sub>STAB</sub>) and R2\_x, R4\_x (R<sub>PROT</sub>) (shown in reference schematic in Chapter 7) should be placed close to the SLIC as possible.

- The capacitor C<sub>DCLP</sub> (C17\_x) need to be placed near the SLIC.

- The EMC capacitors C18\_x, C19\_x and C20\_x need to be placed close to the SLIC pins as possible.

- The resistor R2\_A of the voltage divider for GR-909 support must be placed near to the VINETIC®-2CPE/1CPE device to reduce the length of the VCMIT\_x trace. The R1\_A resistors can be placed near to the line

connector.

# 5.2.2 Routing

- One common ground layer, no separation between analog and digital grounds, is recommended.

- ACP/ACN tracks have to be routed in parallel and symmetrical with small distance; connections via holes should be avoided. A small area of ACP/ACN reduces EMI/EMR.

- · ACP/ACN tracks need to be routed above a GND plane.

- DCP/DCN tracks have to be routed in parallel and symmetrical with small distance; connections via holes need to be avoided.

- The External Noise Filter capacitor in DCP/DCN (C17\_x in Figure 25) is placed close to the SLIC with short traces.

- DCP/DCN tracks need to be routed and placed above a GND plane.

- Distances between the pair of ACN/ACP and the pair of DCN/DCP tracks have to be at least four times greater than the distance of ACN and ACP or DCN and DCP.

- The connection of GND, the battery voltages and all connections to the protection devices have to be low-impedance in order to avoid ground bouncing due to the high impulse currents in case of an overvoltage strike wide tracks or planes are required. A width of at least 15 mil is recommended.

- No digital tracks have to cross or to be placed in parallel to the analog tracks between the VINETIC®-2CPE/1CPE and the SLIC-DC. This includes especially the PCM interface signals and clock signals like FSC, PCL

and MCLK. Further more host controller interfaces including the control signals are not to be routed through

the analog section. It is recommended to route these tracks under the TQFP-package at an inner layer or at

the bottom layer to avoid crosstalk to sensitive analog circuitry.

- For the FSC, PCL and MCLK signals an AC termination at the far end to ground is recommended at the VINETIC®-2CPE/-1CPE (receive side) to avoid ringing. The transmitter side recommends a serial termination.

- The connection from the GNDP pin of the VINETIC<sup>®</sup>-2CPE/-1CPE to the ferrite bead and to the GND plane

must be as short as possible.

The recommendations at the line side are:

- Depending on the protection requirements, the track width from TIP/RING interface to the overvoltage

protector must be chosen accordingly. In practice, a trace width of 16 mil is sufficient to meet the most surge

requirements.

- V<sub>S</sub> and GNDA needs wider traces (15 mil).

**Layout Guide**

Figure 25 Connections between the VINETIC®-2CPE/-1CPE and the SLIC-DC with External Components

When only one channel of the VINETIC®-2CPE is to be used, the not used analog pins must be connected (VCMIT, IT, ITAC, RING and TIP).

In case of a VINETIC®-1CPE Version 2.2 (PEB 3331) is used the pins named ATEST must be connected together.

When a system is developed for one or two channels, the same layout can be used and no additional components may be needed. The board can be mounted differently to have the correct connection for a one channel solution. The same layout can be used, when no channel is used, or all ATEST pins must be connected together.

When the second channel is not used, the SLIC and some external components are not mounted. Other external components have to be modified. The mounting option and the values are shown in **Table 2**. The layout for both solutions is the same.

Table 2 Mounting Option for an unused Channel

| Component | Value              |                                         |  |  |

|-----------|--------------------|-----------------------------------------|--|--|

|           | 2 Channel Solution | 1 Channel Solution (Channel B not used) |  |  |

| C15_2     | 1 μF               | 0 Ω                                     |  |  |

| C16_2     | 18 nF              | Not mounted                             |  |  |

| C17_2     | 4.7 nF             | Not mounted                             |  |  |

CONFIDENTIAL Layout Guide

Table 2 Mounting Option for an unused Channel (cont'd)

| Component | Value              |                                                    |  |  |

|-----------|--------------------|----------------------------------------------------|--|--|

|           | 2 Channel Solution | 1 Channel Solution (Channel B not used) $0 \Omega$ |  |  |

| R15_2     | 499 Ω              |                                                    |  |  |

| R16_2     | 499 Ω              | 0 Ω                                                |  |  |

| R1_2      | 1.5 ΜΩ             | Not mounted                                        |  |  |

| R2_2      | 3.3 kΩ             | 0 Ω                                                |  |  |

| R3_2      | 3.3 kΩ             | 0 Ω                                                |  |  |

| R4_2      | 1.5 ΜΩ             | Not mounted                                        |  |  |

Figure 26 VINETIC®-1CPE Version 2.2 for one Channel

At the PEB 3331 the pins with the name ATEST must be connected together.

### 5.3 Layout Hints for the SLIC-DC

The SLIC-DC has a DC/DC converter as additional circuitry. This converter must be carefully handled in the layout. For the DC/DC converter layout the following rules have to be obeyed:

- The switching transistor needs a heat sink on the board. The heat sink must have an area of 100 mm<sup>2</sup>.

- The value for the sense resistor R12\_x in the reference schematics in **Chapter 7** depends on the ringing requirements of the application as well as on the switching coil used. For ringing requirements up to 5REN, a 0.15  $\Omega$  / 1W / 5% resistors is recommended. A value of 0.27  $\Omega$  / 0.5 W / 5% is recommended for applications with ringing loads up to 3REN ringing.

CONFIDENTIAL Layout Guide

- The traces of the circuitry between SLIC-DC pin VN and the inductor (150  $\mu$ H, including the two 1  $\mu$ F capacitors) must have a width of 15 mil.

- The two 1  $\mu$ F capacitors at the  $V_N$  supply can be of types of X7R, but they must have a voltage rating of 100 V.

- The parts and the traces of the DC/DC part should not be placed near to the Tip and Ring lines, or should otherwise be routed in a separate layer.

- The trace length of VCMIT\_x has to be as short as possible and it may not be routed in the near of the DC/DC converter of SLIC-DC.

- Close connection of the external components to pin EAN, EAO and SWD.

- The lines VS and SENSE to the shunt resistor must be routed as pairs (Figure 19).

- $C_{DCLP}$  (C17\_x) must be placed near to the SLIC-DC.

The decoupling capacitors are placed around the SLIC package at the component side. The routing can be realized in the following way:

- The differential signals ACN/ACP and DCN/DCP are routed at the solder side.

- The digital host interface and the clock signals are routed at the component and solder side and far away from the analog signals.

- The control lines are routed at the component side (top side).

- The VS trace must be routed for each channel as a separate trace and connected near the power supply at a blocking capacitor (star point).

- The GND of the DCDC-high current path must be routed for each channel as a separate trace and connected near the power supply at a blocking capacitor (star point) of the board (as shown in Figure 19).

- · The power supplies are placed in the two inner layers.

The pin SYNC of all SLIC-DC devices in the system can be connected via jumper (0  $\Omega$  resistors) to synchronize the DC/DC converters.

### 5.4 Layout Hints for the SLIC-E

The placement and the layout hints for the VINETIC®-2CPE/-1CPE and the SLIC-DC described in this document in **Chapter 5.2** and **Chapter 5.3** can be used for the SLIC-E as well, however, the layout hints for the DC/DC converter part are obsolete. Therefore, this chapter only describes the components placement of the power supplies  $V_{\text{BATL}}$ ,  $V_{\text{BATH}}$  and  $V_{\text{HR}}$  and the layout hints for this part.

#### 5.4.1 Placement of Power Supply Components

For the placement of the power supply components the following rules have to be obeyed:

- The triple diode package BAS21U has to be placed close to the SLIC-E.

- The decoupling capacitors of V<sub>BATL</sub> and V<sub>BATH</sub> have to be placed close to the diodes.

- The decoupling capacitor of V<sub>HR</sub> has to be placed close to the SLIC-E pin V<sub>HR</sub>.

### 5.4.2 Routing

The power supply must be routed in big traces or better in planes from the power supply to the diodes. The traces between the diodes and the pin of SLIC-E must be routed as wide as possible (e.g. width of 1mm). The voltages between the supplies  $V_{BATL}$  or  $V_{BATH}$  to  $V_{HR}$  can be about 100 V or above. The separation between  $V_{BATL}$  or  $V_{BATH}$  to  $V_{HR}$  must fulfill country specific requirements for clearance and creepage (e.g. UL 60950 [7]).

### 5.4.3 Cooling Area on PCB

The SLIC-E is available in PG-DSO-20 or PG-VQFN-48 package. In the package PG-VQFN-48 a cooling area is required on board. The layout for this package and the cooling area are specified in [4].

**Summary and Design Checklist**

## 6 Summary and Design Checklist

This chapter is divided into 2 parts: the guidelines for the schematic and the guidelines for the layout.

### 6.1 Schematic Guidelines

#### 6.1.1 Power Supply

- Are the power supply tolerances for the VINETIC<sup>®</sup>-2CPE/-1CPE and the SLICs met? (Chapter 4.2 and Chapter 4.3)

- Are the ripple requirements for the VINETIC<sup>®</sup>-2CPE/-1CPE and the SLICs met? ([1])